# Relaxed Logging for Replay of Multithreaded Applications

# Aliaksandra Sankova

Dissertation for the Degree of Master of Information Systems and Computer Engineering

## Jury

President: Advisor: Member: Prof. Daniel Jorge Viegas Gonçalves Prof. Doutor Luís Eduardo Teixeira Rodrigues Prof. Doutor Vasco Miguel Gomes Nunes Manquinho

# Acknowledgements

Firstly, I would like to thank my advisor, Prof. Luis Rodrigues, for guiding and supporting me over this year, and also for patience. I would like to express my gratitude to the members of thesis committee for their feedback and fairness. I would specially like to thank Nuno Machado and Manuel Bravo for the fruitful discussions and their helpful comments, they were constant source of guidance and support on every stage of the research work.

This project has been funded with support from the European Commission. This report reflects the views only of the author, and the Commission cannot be held responsible for any use which may be made of the information contained therein.

> Lisbon, July 2015 Aliaksandra Sankova

For my family, dear friends and colleagues who support me continuously.

# Resumo

A banalização do uso de processadores com vários núcleos oferece novas oportunidades para explorar o paralelismo na programação. Infelizmente, a programação concorrente é uma tarefa inerentemente complexa, sendo frequente a ocorrência de erros no acesso a estruturas de dados partilhadas, erros estes que só se manisfestam quando ocorrem alguns encadeamentos (entremuitos) das instruções das várias tarefas que se executam concurrentemente. Reproduzir o encadeamento exacto que manisfesta o erro pode ser uma tarefa muito complexa e morosa, sem a ajuda de ferramentas adequadas.

Neste contexto, uma das principais técnicas para atingir esse objetivo é a que foi designada por gravação e reprodução, a qual consiste em gravar a informação necessária durante a execução de um programa para capturar o encadeamento que manifesta o erro, de forma a que execução falhada possa ser reproduzida mais tarde. Esta técnica resolve o problema de reprodução do erro, mas, infelizmente, em muitos casos acarreta uma diminuição substancial no desempenho da execução da aplicação, devido ao custo da tarefa de gravação.

Esta dissertação apresenta um estudo das abordagens existentes para gravação e reprodução, reflete sobre as vantagens e limitações de cada sistema e propõe uma nova abordagem que tenta reduzir o custo de gravação, sem onerar em demasia o processo de reprodução. São apresentados resultados da avaliação de um protótipo desenvolvido para validar as ideias propostas.

# Abstract

The advent of multi-core processors brought new opportunity to exploit parallelism in programs. However, developing concurrent programs is a sophisticated task, due the new type of bugs that may appear and that may be very difficult to find and to correct. In particular, when multiple threads access shared memory, a buggy parallel program can lead to subtle data races that generate errors in some particular thread interleavings. There is a growing interest on building tools that help to reproduce such interleavings, helping the programmer to correct the code.

One of the main techniques to achieve this goal is what has been called *record and replay*: it consists of logging relevant information during the execution of a program that allows the interleaving that causes the bug to be reproduced later. This technique solves the problem of bug reproduction but, unfortunately, in many cases it introduces a substantial slowdown in the execution of the application.

This dissertation presents a study of existing approaches to record and replay, reflects on trade-offs and decisions of each system, and proposes a new approach of relaxed logging that aims at reducing the cost of the record phase without introducing a substantial increase in the time required to execute replay phase. We have implemented a prototype to validate these ideas and have evaluated it using several benchmarks.

# Palavras Chave Keywords

# Palavras Chave

gravação e reprodução aplicações paralelas

- erros de concurrência

- depuração de código

- ferramentas de software

# Keywords

record and replay parallel applications concurrency bugs debugging software tools

# Contents

| 1        | Intr           | oducti | on                             | 3  |

|----------|----------------|--------|--------------------------------|----|

|          | 1.1            | Motiva | ation                          | 3  |

|          | 1.2            | Contri | butions                        | 5  |

|          | 1.3            | Result | S                              | 5  |

|          | 1.4            | Resear | rch History                    | 5  |

|          | 1.5            | Struct | ure of the Document            | 6  |

| <b>2</b> | $\mathbf{Rel}$ | ated V | Vork                           | 7  |

|          | 2.1            | Record | d and Replay                   | 7  |

|          |                | 2.1.1  | Record Phase                   | 7  |

|          |                | 2.1.2  | Replay Phase                   | 8  |

|          |                | 2.1.3  | Why is it important?           | 8  |

|          | 2.2            | Altern | atives                         | 9  |

|          | 2.3            | Challe | nges                           | 10 |

|          |                | 2.3.1  | Non Determinism                | 10 |

|          |                |        | 2.3.1.1 Input Non-determinism  | 10 |

|          |                |        | 2.3.1.2 Memory Non-determinism | 11 |

|          |                | 2.3.2  | Runtime Overhead               | 12 |

|          |                | 2.3.3  | Log Size                       | 12 |

|          |                | 2.3.4  | Security Issues                | 13 |

| 2.4 | Desigr | h Choices  |                           | 13 |

|-----|--------|------------|---------------------------|----|

|     | 2.4.1  | Impleme    | entation approach         | 13 |

|     |        | 2.4.1.1    | Hardware-Only Systems     | 13 |

|     |        | 2.4.1.2    | Hardware-Software Systems | 14 |

|     |        | 2.4.1.3    | Software-Only Systems     | 14 |

|     | 2.4.2  | Record a   | and Replay Approach       | 14 |

|     |        | 2.4.2.1    | Content-Based Approach    | 15 |

|     |        | 2.4.2.2    | Order-Based Approach      | 15 |

|     |        | 2.4.2.3    | Search-Based              | 15 |

|     | 2.4.3  | Determi    | nism Level                | 16 |

|     |        | 2.4.3.1    | Value Determinism         | 16 |

|     |        | 2.4.3.2    | Output Determinism        | 17 |

|     |        | 2.4.3.3    | Path Determinism          | 17 |

|     | 2.4.4  | Other ch   | noice criteria            | 17 |

| 2.5 | Examj  | ple Syster | ns                        | 18 |

|     | 2.5.1  | Hardwar    | re-Only Systems           | 18 |

|     |        | 2.5.1.1    | FlightDataRecorder        | 19 |

|     |        | 2.5.1.2    | ReRun                     | 20 |

|     |        | 2.5.1.3    | DeLorean                  | 20 |

|     | 2.5.2  | Hybrid S   | Systems                   | 21 |

|     |        | 2.5.2.1    | Саро                      | 21 |

|     | 2.5.3  | Software   | e-Only Systems            | 21 |

|     |        | 2.5.3.1    | Instant Replay            | 22 |

|     |        | 2.5.3.2    | DeJavu                    | 23 |

|   |                                               |                                                             | 2.5.3.3 RecPlay .                                                                                                                                             |                                                            |                        |                     |                       |                                       |         |           | 23                                           |

|---|-----------------------------------------------|-------------------------------------------------------------|---------------------------------------------------------------------------------------------------------------------------------------------------------------|------------------------------------------------------------|------------------------|---------------------|-----------------------|---------------------------------------|---------|-----------|----------------------------------------------|

|   |                                               |                                                             | 2.5.3.4 JaRec                                                                                                                                                 |                                                            |                        |                     |                       |                                       | •••     |           | 23                                           |

|   |                                               |                                                             | 2.5.3.5 iDNA                                                                                                                                                  |                                                            |                        |                     |                       |                                       |         |           | 24                                           |

|   |                                               |                                                             | 2.5.3.6 LEAP                                                                                                                                                  |                                                            |                        |                     |                       |                                       |         |           | 24                                           |

|   |                                               |                                                             | 2.5.3.7 ORDER                                                                                                                                                 |                                                            |                        |                     |                       |                                       |         |           | 25                                           |

|   |                                               |                                                             | 2.5.3.8 CARE                                                                                                                                                  |                                                            |                        |                     |                       |                                       |         |           | 26                                           |

|   |                                               |                                                             | 2.5.3.9 PRES                                                                                                                                                  |                                                            |                        |                     |                       |                                       |         |           | 27                                           |

|   |                                               |                                                             | 2.5.3.10 ODR                                                                                                                                                  |                                                            |                        |                     |                       |                                       |         |           | 27                                           |

|   |                                               |                                                             | 2.5.3.11 STRIDE                                                                                                                                               |                                                            |                        |                     |                       |                                       |         |           | 28                                           |

|   |                                               |                                                             | 2.5.3.12 CLAP                                                                                                                                                 |                                                            |                        |                     |                       |                                       | •••     |           | 29                                           |

|   |                                               | 2.5.4                                                       | Example of Logs P                                                                                                                                             | roduced by Di                                              | fferent Sys            | stems .             |                       |                                       | •••     |           | 30                                           |

|   | 2.6                                           | Summ                                                        | ary                                                                                                                                                           |                                                            |                        |                     |                       |                                       | •••     |           | 32                                           |

|   |                                               |                                                             |                                                                                                                                                               |                                                            |                        |                     |                       |                                       |         |           |                                              |

| 3 | OR                                            | EO                                                          |                                                                                                                                                               |                                                            |                        |                     |                       |                                       |         |           | 37                                           |

| 3 | <b>OR</b><br>3.1                              |                                                             | ale                                                                                                                                                           |                                                            |                        |                     |                       |                                       |         |           |                                              |

| 3 |                                               | Ratio                                                       | ale                                                                                                                                                           |                                                            |                        |                     |                       |                                       |         |           | 37                                           |

| 3 | 3.1                                           | Ration<br>OREC                                              |                                                                                                                                                               | components .                                               |                        |                     |                       |                                       | •••     |           | 37<br>38                                     |

| 3 | 3.1<br>3.2                                    | Ration<br>OREC                                              | Architecture and C                                                                                                                                            | Components .                                               |                        |                     |                       | <br>                                  |         |           | 37<br>38                                     |

| 3 | 3.1<br>3.2                                    | Ration<br>OREC<br>Trade                                     | Architecture and C                                                                                                                                            | Components .<br>                                           | · · · · · ·            | <br>                | <br>                  | · · · ·                               | •••     | · · · · · | 37<br>38<br>40                               |

| 3 | 3.1<br>3.2                                    | Ration<br>OREC<br>Trade-<br>3.3.1                           | Architecture and C<br>offs in OREO<br>Gains on the Recor                                                                                                      | Components .<br><br>d Phase<br>'RIDE's Linkaş              | <br><br>ge Inferen     | <br><br>ce Mech     | <br><br>anism         | <br><br>                              | · · ·   | · · · · · | 37<br>38<br>40<br>40                         |

| 3 | 3.1<br>3.2                                    | Ration<br>OREC<br>Trade<br>3.3.1<br>3.3.2<br>3.3.3          | Architecture and C<br>offs in OREO<br>Gains on the Recor<br>Implications for ST                                                                               | Components .<br><br>d Phase<br>'RIDE's Linkag<br>blay      | <br><br>ge Inferen<br> | <br><br>ce Mech<br> | <br><br>anism<br>     | · · · ·                               | · · ·   | · · · · · | 37<br>38<br>40<br>40<br>40                   |

| 3 | <ul><li>3.1</li><li>3.2</li><li>3.3</li></ul> | Ration<br>OREC<br>Trade<br>3.3.1<br>3.3.2<br>3.3.3          | Architecture and C<br>offs in OREO<br>Gains on the Recor<br>Implications for ST<br>Using SMT for Rep                                                          | Components .<br><br>d Phase<br>'RIDE's Linkag<br>blay      | <br><br>ge Inferen<br> | <br><br>ce Mech<br> | <br><br>anism<br>     | · · · · · · · · · · · · · · · · · · · | · · · · | · · · · · | 37<br>38<br>40<br>40<br>40<br>42             |

| 3 | <ul><li>3.1</li><li>3.2</li><li>3.3</li></ul> | Ration<br>OREC<br>Trade<br>3.3.1<br>3.3.2<br>3.3.3<br>Const | Architecture and C<br>offs in OREO<br>Gains on the Recor<br>Implications for ST<br>Using SMT for Rep<br>aint Model<br>Intra-thread Constr                     | Components .<br><br>d Phase<br>'RIDE's Linkag<br>blay      | <br><br>ge Inferen<br> | <br><br>            | <br><br>anism<br>     | · · · ·<br>· · · ·<br>· · · ·         |         | · · · · · | 37<br>38<br>40<br>40<br>40<br>42<br>43<br>43 |

| 3 | <ul><li>3.1</li><li>3.2</li><li>3.3</li></ul> | Ration<br>OREC<br>Trade<br>3.3.1<br>3.3.2<br>3.3.3<br>Const | Architecture and C<br>offs in OREO<br>Gains on the Recor<br>Implications for ST<br>Using SMT for Rep<br>aint Model<br>Intra-thread Constr<br>3.4.1.1 Memory C | Components .<br><br>rd Phase<br>'RIDE's Linkaş<br>blay<br> |                        |                     | <br><br>anism<br><br> | · · · ·<br>· · · ·<br>· · · ·         |         | · · · · · | 37<br>38<br>40<br>40<br>40<br>42<br>43<br>43 |

|   |     |         | 3.4.2.1 Read-Write Constraints                                                                                          | 44 |

|---|-----|---------|-------------------------------------------------------------------------------------------------------------------------|----|

|   |     |         | 3.4.2.2 Synchronization Order Constraints                                                                               | 45 |

|   |     | 3.4.3   | Our model versus CLAP                                                                                                   | 46 |

|   | 3.5 | Lifecy  | cle of the program on example $\ldots$ | 46 |

|   |     | 3.5.1   | Transformer Output                                                                                                      | 46 |

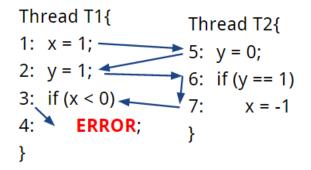

|   |     | 3.5.2   | Recorder Output                                                                                                         | 47 |

|   |     | 3.5.3   | Offline Resolver Output                                                                                                 | 47 |

|   |     | 3.5.4   | Replayer                                                                                                                | 50 |

|   | 3.6 | Impler  | mentation Details                                                                                                       | 51 |

|   |     | 3.6.1   | Transformer                                                                                                             | 51 |

|   |     | 3.6.2   | Recorder                                                                                                                | 52 |

|   |     | 3.6.3   | Offline-Resolver                                                                                                        | 52 |

|   |     | 3.6.4   | Replayer                                                                                                                | 53 |

|   | 3.7 | Summ    | ary                                                                                                                     | 53 |

| 4 | Eva | luatior | 1                                                                                                                       | 55 |

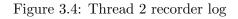

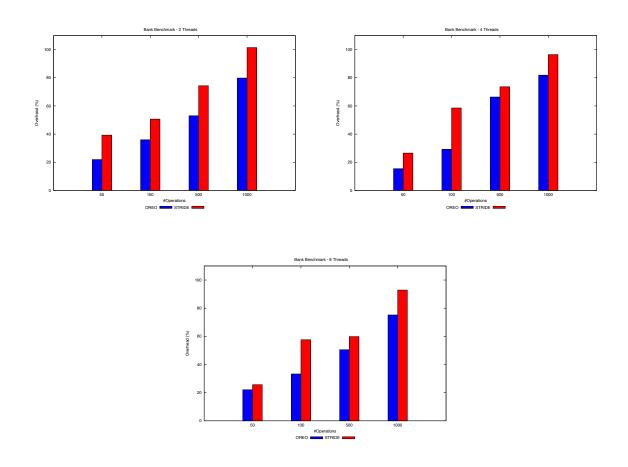

|   | 4.1 | Bank    | Micro-benchmark                                                                                                         | 56 |

|   |     | 4.1.1   | Recording Overhead                                                                                                      | 56 |

|   |     | 4.1.2   | Log Sizes                                                                                                               | 57 |

|   |     | 4.1.3   | Write Conflicts                                                                                                         | 58 |

|   |     | 4.1.4   | Inference Time                                                                                                          | 58 |

|   | 4.2 | Third-  | Party Benchmarks                                                                                                        | 59 |

|   |     | 4.2.1   | Recording Overhead                                                                                                      | 59 |

|   |     | 4.2.2   | Log Sizes                                                                                                               | 60 |

|   |     | 4.2.3   | Write Conflicts                                                                                                         | 60 |

|    |       | 4.2.4   | Infere        | ence Ti | me | <br> | <br> | <br>    | <br> | <br> | <br> | • • | •   | <br> | 60 |

|----|-------|---------|---------------|---------|----|------|------|---------|------|------|------|-----|-----|------|----|

|    | 4.3   | Summ    | ary .         |         |    | <br> | <br> | <br>    | <br> | <br> | <br> |     |     | <br> | 60 |

| 5  | Con   | nclusio | $\mathbf{ns}$ |         |    |      |      |         |      |      |      |     |     |      | 63 |

|    | 5.1   | Conclu  | usions        |         |    | <br> | <br> | <br>• • | <br> | <br> | <br> |     | ••• | <br> | 63 |

| Bi | bliog | raphy   |               |         |    |      |      |         |      |      |      |     |     |      | 69 |

# List of Figures

| 2.1 | Level of determinism, provided in record and replay systems                | 16 |

|-----|----------------------------------------------------------------------------|----|

| 2.2 | Hardware-only techniques (Source: Intel Corporation, 2009)                 | 21 |

| 2.3 | Logical representation of Capo                                             | 22 |

| 2.4 | Example of thread interleavings                                            | 30 |

| 3.1 | Components of proposed system                                              | 38 |

| 3.2 | Example of thread interleavings                                            | 46 |

| 3.3 | Thread 1 recorder log                                                      | 48 |

| 3.4 | Thread 2 recorder log                                                      | 48 |

| 4.1 | Recording overhead $(\%)$ for OREO and STRIDE for benchmark Bank, executed |    |

|     | with 2, 4, and 8 threads. Results are averaged over 5 runs                 | 57 |

# List of Tables

| 2.1 | Logs used in various systems                                                       | 31 |

|-----|------------------------------------------------------------------------------------|----|

| 2.2 | Summary of the presented systems                                                   | 33 |

| 4.1 | Log sizes for OREO.                                                                | 58 |

| 4.2 | Amount of time required to solve the constraint model with the read-write linkages |    |

|     | and produce a legal schedule                                                       | 58 |

| 4.3 | Results for third-party benchmarks.                                                | 59 |

# Acronyms

${\bf OS}\,$  Operation System

**DMA** Direct Memory Access

${\bf SMT}$  Satisfiability modulo theories

${\bf SMP}$  Symmetric Multiprocessing

${\bf SPE}\,$  Shared Program Element

${\bf JSON}$ JavaScript Object Notation

${\bf JVM}\,$ Java Virtual Machine

$\mathbf{SC}$  Sequential Consistency

${\bf PSO}\,$  Partial Store Ordering

${\bf TSO}~{\rm Total}~{\rm Store}~{\rm Ordering}$

# Introduction

This thesis addresses the problem of reproducing bugs in concurrent programs that rely on the shared memory paradigm. We study mechanisms to ensure such bugs will appear during re-execution in a way that will empower the programmer to infer the nature of this bug and therefore allow fixing it.

# 1.1 Motivation

The possibility to reproduce bugs in concurrent programs is important and essential when we develop a software that exploits multithreading opportunities offered by multi-core processors. It can be used not only for debugging but also to treat security vulnerabilities and analyse performance. Our targeted object of study, concurrent programs that rely on the shared memory paradigm, can be characterized by different sequential threads that execute in parallel, quite often in different cores of a multi-processor, communicating with each other by reading and writing in shared variables. In order to coordinate and communicate among each other, such threads need to use explicit synchronization, such as *locks* or *semaphores*(Dijkstra 2002). In particular, when accessing shared data, the logic of the program must ensure that the threads use the required synchronization to avoid *data races* (Netzer and Miller 1989). A data race occurs when different threads access a shared data structure without synchronization, and at least one of those accesses is a write. Data races can be avoided by the correct use of synchronization primitives however these primitives are hard to master. An incorrectly placed or missing synchronization primitive may not only eliminate the race but even create other bugs, for example introduce deadlocks (Coffman, Elphick, and Shoshani 1971). Furthermore, the interleavings that cause the bug may happen only in some rare circumstances, and be very hard to reproduce. This makes the debugging of concurrent programs an extremely difficult and tedious task. In this context we studied techniques and tools that simplify the reproduction of concurrency bugs and came up with an idea of how the state of the art could be improved. Delving into the topic,

one of the main techniques to achieve the reproduction of concurrency bugs is what has been called record and replay (Choi and Srinivasan 1998; Georges, Christiaens, Ronsse, and De Bosschere 2004; Ronsse and De Bosschere 1999; LeBlanc and Mellor-Crummey 1987a; Park, Zhou, Xiong, Yin, Kaushik, Lee, and Lu 2009; Altekar and Stoica 2009; Huang, Liu, and Zhang 2010; Yang, Yang, Xu, Chen, and Zang 2011; Zhou, Xiao, and Zhang 2012; Jiang, Gu, Xu, Ma, and Lu 2014) (or *deterministic replay* (Huang, Zhang, and Dolby 2013)). Record and replay relies in instrumenting the application in order to record all sources of non-determinism at runtime, including inputs, interrupts, signals, and scheduling decisions. For multi-core environments, it is also necessary to record the order by which different threads have accessed shared variables. This way, deterministic replay can be achieved by re-executing the application while enforcing all points of non-determinism to comply with the information stored in the log. Previous work that studied the problem of reproducing bugs in concurrent programs discovered that faithfully logging a concurrent program's execution requires inserting additional synchronization (to ensure that the thread interleaving is correctly traced). This, in combination with the large amount of information that may be required to be captured, can induce an unacceptable slowdown in the application (Georges, Christiaens, Ronsse, and De Bosschere 2004; Ronsse and De Bosschere 1999; Altekar and Stoica 2009; Huang, Liu, and Zhang 2010). To address this issue, some approaches attempted to reduce the amount of synchronization used to register the log, the amount of information included in the log, or even both. For instance, one can trace only partial information during the production run and then, at replay time, use search techniques to infer thread interleavings that are compliant with the (partial) log information (Park, Zhou, Xiong, Yin, Kaushik, Lee, and Lu 2009; Jiang, Gu, Xu, Ma, and Lu 2014). However, since reducing the amount of information logged hinders the replay determinism, the challenge lies in identifying the best trade-off between recording cost and inference time.

This work focus on exploring a relaxation of the logging procedure, allowing to avoid synchronization when recording concurrent accesses to shared variables, in order to lower the recording cost. To allow this relaxation, we also devise a replay mechanism that can search the different interleavings that are compliant with the information stored in order to find de sequence that reproduces the bug.

#### 1.2. CONTRIBUTIONS

## **1.2** Contributions

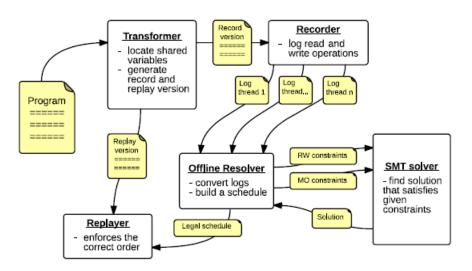

This work studies the main techniques to achieve the reproduction of concurrency bugs and explores a novel combination of techniques to achieve this goal. We decided to name our proposal Optimistic REcOrd and REplay (OREO). We relax the recording order of write operations on shared state. This makes the record operation more efficient at the cost of a more sophisticated replay phase. To address the challenges of finding the interleaving that causes the bug from the relaxed log we resort to SMT solvers, by encoding the information recorded as a set of constraints that any buggy interleaving must satisfy. More precisely, the thesis makes the following contributions:

- It introduces the new technique to record and replay concurrent programs.

- From an experimental evaluation of the proposed technique it provides insights on its advantages and limitations.

# 1.3 Results

The results of this work can be enumerated as follows:

- 1. a specification of the algorithms to trace, collect and analyze information in order to replay concurrent executions;

- 2. explanation of a constraint model used between the system and SMT solver in order to get a faithful replay;

- 3. an implementation of a prototype of this system;

- 4. experimental evaluation using real-world applications and third-party benchmarks with concurrency bugs.

## 1.4 Research History

The aim of our work was to explore the potential benefits that could be achieved from relaxing the logging phase, in particular, by avoiding locks when storing the order of write operations. To address the replay based on relaxed information we first attempted to derive variants of the replay techniques described by Zhou, Xiao, and Zhang (2012). However, this approach proved to be unfeasible. Therefore, we opted to resort to the use of SMT solvers to find the interleaving that reproduces the bug, by encoding the information collected during the record phase as a set of constraints that the faulty schedule needs to satisfy. This work was performed in the fruitful collaboration with Nuno Machado and Manuel Bravo.

## 1.5 Structure of the Document

The rest of this document is organized as follows. For self-containment, Section 2 provides an introduction to record and replay and describes previous work related to the problems that we introduce. Chapter 3 presents the architecture and algorithms used in the proposed solution and Chapter 4 presents the results of the experimental evaluation study. Finally, Chapter 5 concludes this document by summarizing its main points and discusses future work.

# Related Work

This chapter provides a description of the record and replay technique, a justification for its existence and alternatives to this approach, followed by a review of the related work that is relevant to the project. Section 2.1 introduces us to basic concepts of the technique, Section 2.2 presents some alternative approaches and Section 2.3 shows us main challenges; Section 2.4 describes the design choices and trade-offs that one has to take into account when implementing this kind of system; Section 2.5 presents an overview of the most relevant record and replay solutions and depicts the state of the art; Section 2.6 sums up the chapter.

## 2.1 Record and Replay

Record and replay of multithreaded applications (also known as deterministic replay) is a popular technique to reproduce non-trivial bugs, in particular bugs of non-deterministic nature. The goal of this technique is to allow a given execution of a program to be faithfully reproduced, which requires the ability to reproduce not only the inputs provided to the program, but also all non-deterministic events, such as interrupts and thread interleavings. In general, techniques that provide deterministic replay operate in two distinct phases: record and replay, which are better explained in Subsections 2.1.1 and 2.1.2 respectively.

## 2.1.1 Record Phase

Record phase can be further divided into two sub-parts, decision-making and data processing:

- define the relevant data: suggest inputs and shared variables that are important for future assurance of reproduction to follow the same steps as the original run.

- log suggested information: put into a trace file values of the inputs and shared variables, selected as relevant.

In this phase, important questions are granularity of log (discussed in Subsection 2.3.3) and performance overhead (discussed in Subsection 2.3.2).

#### 2.1.2 Replay Phase

The *Replay phase* can also be divided into two sub-parts, consulting and analysing the trace and finally, re-execution:

- *read the log*: consult the trace, produced on the *Record phase*, we decide which steps we will take to repeat the original run. It may require transformation of the existing log to a new replay-specified log with usage of axillary data structures.

- *reproduce the execution*: re-execute the program in a controlled manner, ensuring that the run reconstructs the original execution. In other words, we force the replay of non-deterministic events that we recorded beforehand.

In this phase, important questions are performance overhead, referred together with recording overhead in Subsection 2.3.2, and the ability to reproduce the original run at all.

#### 2.1.3 Why is it important?

Deterministic replay can be used for a wide range of applications. The most common among them are the following (Pokam, Pereira, Danne, Yang, King, and Torrellas 2009):

- **Debugging** Deterministic replay is very useful in debugging and testing as it provides a possibility to hold cyclic re-executions and, therefore, travel in time within the program run. As a debug measure, cyclic re-executions may introduce an illusion of reverse execution (Boothe 2000; Feldman and Brown 1988; Zelkowitz 1973) and help to detect faults in various programs, sequential and with high probability in non-deterministic executions (Georges, Christiaens, Ronsse, and De Bosschere 2004; LeBlanc and Mellor-Crummey 1987a; LeBlanc and Mellor-Crummey 1987b).

- **Security** The possibility to reproduce execution can be used to search exploits of newly discovered vulnerabilities (Joshi, King, Dunlap, and Chen 2005) analyse status of the system

under attack (Dunlap, King, Cinar, Basrai, and Chen 2002; King, Dunlap, and Chen 2003) or efficiently perform expensive security checks (Chow, Garfinkel, and Chen 2008).

**Fault-tolerance** Developers can use deterministic replay to recover the state of the system after a crash (Bressoud and Schneider 1996).

## 2.2 Alternatives

To better justify why we decided to focus on deterministic replay, we briefly present other techniques (even though we are not addressing them in this work):

- **Online Debugging** This is a classical way to debug a program that is known from a majority of IDEs, where inline assertions and break points are used. Such an approach normally requires the developer to have an idea of of a bug's nature, which may not work when the bugs are introduced by data races.

- **Execution synthesis** Automated version of online debugging, this technique relies on bug reports and static analysis (Zamfir and Candea 2010). It does not require runtime tracing of a program. Hence, it introduces no runtime overhead which can be seen as its main advantage. However, there are some bug reports that the system cannot process and, therefore, some bugs that the system cannot reproduce. Limitations of bug reports do not exist in the deterministic replay approach.

- Fault Localization Naturally after failing reproductions, there is a technique that aims to discover the bugs and their nature before making an attempt to reproduce them. Many systems use various approaches: static or dynamic analysis (Lu, Park, Hu, Ma, Jiang, Li, Popa, and Zhou 2007), model-checking (Brat, Havelund, Park, and Visser 2000), etc. Such systems are prone to omission such as marking some bugs falsely positive or vice versa, treating normal code falsely negative.

- **Deterministic Execution** Close to deterministic replay, deterministic execution provides the same ability to reproduce a program with main difference in targeted reduction of inherent non-determinism of the application. Kendo (Olszewski, Ansel, and Amarasinghe 2009a) tracks the progress of each thread using performance counters to construct a deterministic

logical time that is used to compute an interleaving of shared data accesses. CLAP (?) tracks thread local execution paths. The main drawback of such approach is its tendency to avoid such sources of non-determinism as user input.

Log-based Debugging Basing on logged information only, log-based debugging automatically infers possible cause of the bug. Real systems use machine learning techniques and data mining (Xu, Huang, Fox, Patterson, and Jordan 2009). The advantage that these systems provide in avoiding runtime overhead costs by operating offline is offset by the huge traces or by inability to reconstruct a detailed execution state due to lack of information.

## 2.3 Challenges

Although simple in theory, building a deterministic replay system poses several issues. Within the following subsections we discuss the most relevant challenges that need to be addressed in the context of record and replay.

#### 2.3.1 Non Determinism

The main difficulty of concurrency bugs reproduction is their non-deterministic nature, which, from time to time, makes them disappear when specific interleaving does not occur. There are many sources of non-determinism in a system (Tanenbaum, Austin, and Chandavarkar 2013). Deterministic replay address this issue by capturing them, however, what to consider as nondeterministic input depends on which level we are operating on. As no system deals with all forms of non-determinism (Cornelis, Georges, Christiaens, Ronsse, Ghesquiere, and Bosschere 2003) and different systems target different levels of abstraction, let us consider the user and system level for better understanding, which kind of events we will capture after selecting particular granularity. We also differentiate input non-determinism and memory non-determinism.

#### 2.3.1.1 Input Non-determinism

**User Level** At the user level, sources of non-determinism originate from the operating system (OS). Among them are certain system calls, signals, special architecture instructions (Pokam, Pereira, Danne, Yang, King, and Torrellas 2009).

- System Calls: various system calls become non-deterministic when they depend on external sources, such as information from a network card or a disk. As an example we can mention Unix system call *gettimeofday()*.

- Signals: possibility to receive asynchronous signals makes the program nondeterministic.

- Special Architectural Instructions: on some architectures various instructions are considered as non-deterministic. As an example we can mention the *rdtsc* x86 instruction, which reads the CPU's timestamp, or *rdpmc* x86, which returns value of the performance counter.

- System Level: At the system level, major sources of non-determinism are signals from I/O devices, hardware interrupts, and writes performed by Direct Memory Access (Pokam, Pereira, Danne, Yang, King, and Torrellas 2009).

- I/O: majority of instructions consider memory mapped I/O, which does not guarantee that reads from these devices can be repeated. Therefore, they have to be recorded.

- Hardware Interrupts: used to notify the processor that some data can be consumed, hardware interrupts change the control flow of execution in an asynchronous way. A recorder needs to log the point at which the interrupt has arrived and the source of the interrupt (e.g. disk I/O, network I/O, timer interrupt, etc).

- Direct Memory Access (DMA): these are operations of writing directly to memory without process awareness. The recorder needs to log all the values written by DMA with respect to their timing.

#### 2.3.1.2 Memory Non-determinism

Memory interleaving input non-determinism appears in concurrent execution. However, in multi-core machines, an additional source of non-determinism is present. This is the order in which all threads in the system access shared memory, known as memory races. Having memory races in execution means that during various runs of a program different threads may end up winning the race when trying to access a piece of shared memory. They occur between synchronization operations (synchronization races) or between data accesses (data races) (Pokam, Pereira, Danne, Yang, King, and Torrellas 2009).

- Synchronization Races: are used to determine the order of other operations in a program's execution: locks that provide mutual exclusion in a critical region, etc. However, the order in which synchronization operations themselves are executed is non-deterministic.

- Data Races: occur when there are two or more unsynchronized concurrent accesses to the same shared memory location and at least one of them is to perform a write operation.

To provide deterministic replay of any concurrent program on a single-processor system, it is enough to record thread order decisions made by the scheduler (Ronsse and De Bosschere 1999). On multiprocessor machine this will not be sufficient as threads actually execute simultaneously on different processors. Thus, the solution is to manage capture the outcome of each thread shared access, which is not trivial do to efficiently.

### 2.3.2 Runtime Overhead

The record phase may induce a non-negligible overhead during the execution of a program. The more information is included in the log, i.e., the finer the granularity of logging, the easier to ensure deterministic replay, but the larger it is the recording overhead. Approaches that opt to log less information, i.e., that perform logging at a coarser granularity, are less expensive, but make it harder to reproduce the original schedule in reasonable time. As such, there is an inherent trade-off between *logging accuracy* and *replay efficiency*. According to the taxonomy (Cornelis, Georges, Christiaens, Ronsse, Ghesquiere, and Bosschere 2003), good deterministic replay should be *time efficient* - the performance overhead should be minimized in order to maintain the use of the program acceptable.

#### 2.3.3 Log Size

On the record phase we are saving information to some trace file or log. This log should have adequate size and the amount of space, dedicated to store that log, should be minimal. Hence, another relevant metric of quality of deterministic replay systems is the *space efficiency* during the record phase (Cornelis, Georges, Christiaens, Ronsse, Ghesquiere, and Bosschere 2003) - the size of the log file containing the non-deterministic events captured during the recording phase should be minimized as well.

#### 2.3.4 Security Issues

When logging information during production runs, one must take into account that some collected data may be sensitive. This raises security and privacy issues if the log needs to be shared with others (for instance, if the log is sent to the developer). Therefore, the degree of user data disclosure during recording is also considered to be important when devising record and replay solutions. Despite that, in our work, we do not explicitly address this concern, because it is somewhat orthogonal to the techniques that we plan to experiment with.

## 2.4 Design Choices

A large diversity of techniques has been proposed to perform record and replay. This section concerns a brief taxonomy, where the main design choices regarding the development of a deterministic replay system have been identified, particularly, how the solution is implemented, approach taken to record and reproduce an execution of the program and level of determinism provided.

#### 2.4.1 Implementation approach

Deterministic replay techniques are usually classified according to the amount of specialized support that is built in hardware for this particular purpose. In particular, we consider three different types of systems. For self-containment purposes, in Section 2.6, we will make an overview of systems using the three techniques above. However, our work we will be mainly focusing on software-only approaches as hardware modifications reduced by other two approaches nowadays are only available as simulations.

#### 2.4.1.1 Hardware-Only Systems

These types of systems are able to provide deterministic replay with significantly lower recording overhead than in software solutions, supporting the replay of data-races on multiprocessors in particular. Examples of hardware-only implementations that are considered as the state of the art are given in (Montesinos, Ceze, and Torrellas 2008; Xu, Bodik, and Hill 2003). Unfortunately, bringing these concepts to reality requires expensive non-commodity hardware. Implementing deterministic replay on hardware ties the approach to a particular architecture.

#### 2.4.1.2 Hardware-Software Systems

This is hybrid approach that combines both hardware and software techniques, aiming at the reduction of necessary hardware modifications preserving gain in the recording time. The state of the art system (Montesinos, Hicks, King, and Torrellas 2009) represents this search for a sweet-spot between hardware cost and efficiency but, like pure hardware solutions, tie the approach to specific architectures.

### 2.4.1.3 Software-Only Systems

Despite of not being as efficient as the ones above, software-only implemented systems are the most common tendency in research of deterministic replay due to their advantage of being more general. Looking for support of deterministic replay on heterogeneous architecture, many solutions have been implemented so far (Georges, Christiaens, Ronsse, and De Bosschere 2004; Ronsse and De Bosschere 1999; Choi and Srinivasan 1998; LeBlanc and Mellor-Crummey 1987a; Olszewski, Ansel, and Amarasinghe 2009b; Bhansali, Chen, De Jong, Edwards, Murray, Drinić, Mihočka, and Chau 2006; Huang, Liu, and Zhang 2010; Yang, Yang, Xu, Chen, and Zang 2011; Jiang, Gu, Xu, Ma, and Lu 2014; Huang, Liu, and Zhang 2010; Altekar and Stoica 2009; Park, Zhou, Xiong, Yin, Kaushik, Lee, and Lu 2009; Zhou, Xiao, and Zhang 2012). They can be applied to many different off-the-shelf architectures. Some of them (Huang, Liu, and Zhang 2010; Zhou, Xiao, and Zhang 2012) are considered as the state of the art.

#### 2.4.2 Record and Replay Approach

Another way of classifying record and replay systems consists of looking at the type of information that is recorded in the log. Here, it is possible to distinguish approaches as contentbased, order-based, and search-based (Cornelis, Georges, Christiaens, Ronsse, Ghesquiere, and Bosschere 2003).

#### 2.4.2.1 Content-Based Approach

Content-based systems are also called data-driven as they record and replay the data read by each instruction. Literally, they log the values of all the relevant inputs and shared variables read by each thread, such that the exact same values can be used during replay. The major drawback of this approach is that it generates very large logs and may induce severe slowdowns in the execution of the program, making approach inefficient (Bhansali, Chen, De Jong, Edwards, Murray, Drinić, Mihočka, and Chau 2006).

### 2.4.2.2 Order-Based Approach

Instead of tracking the values of variables, order-based systems track the control flow of the program (such as timing of interactions with program files or I/O channels) from a given initial state. these types of systems are also called control-driven. According to this approach it is not necessary to record every instruction to replay an execution, which allows to reduce the amount of traced data. However, read and write accesses to shared memory locations still need to be tracked in order to support the reproduction of the thread interleaving. Such tracking is called the *exact* linkage between reads and writes into shared memory. This technique imposes lower overhead on record phase and creates smaller amounts of logs comparing to content-based solutions. The main challenge with this approach is to ensure that the initial state of the program is exactly the same in both the original and the reproduction run. Unfortunately, the initial state may often depend on the availability of external resources such as cores in multicore processors, that could affect the internal state of the program being replayed. Furthermore, to ensure that the log faithfully captures the thread read-write linkage, it is generally necessary to introduce additional synchronization during the record phase. Thus, even if order-based approaches represent an improvement over pure content-based approaches, most systems implemented with this approach still induce a large overhead at runtime (Altekar and Stoica 2009; Huang, Liu, and Zhang 2010).

#### 2.4.2.3 Search-Based

This approach was created with a goal to mitigate an extremely high cost for some applications incurred by assurance of bug reproducibility in every execution, which sometimes would cause up to 100x slowdown (Park, Zhou, Xiong, Yin, Kaushik, Lee, and Lu 2009). The main idea is to not log the exact thread read-write linkage and instead, to rely on a post-recording phase to construct a feasible interleaving from a *partial log* (Altekar and Stoica 2009; Park, Zhou, Xiong, Yin, Kaushik, Lee, and Lu 2009; Zhou, Xiao, and Zhang 2012) or to infer the missing information(Huang, Zhang, and Dolby 2013). This way, it is possible to substantially reduce the recording overhead at the cost of smaller determinism guarantees and a potentially longer replay. However, since the search space increases exponentially with the amount of missing information regarding the ordering of thread shared accesses, search-based approaches need to carefully balance the inference time and the recording overhead. Since pure content- and order-based systems incur an overhead is too high to be practical, most recent solutions have adopted a search-based approach. Our solution follows this trend, as well.

### 2.4.3 Determinism Level

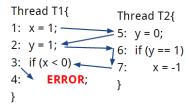

Very often producing the exact execution on replay is an excessively expensive task, thus systems calibrate the level of determinism they provide depending on the execution they try to replay and problems they try to tolerate. Some of these levels of determinism "granularity" are presented below, and for better understanding are accompanied with code examples in Figure 2.1.

| Original run       | Value determinism  | Output determinism               | Path determinism | Non-determinism    |

|--------------------|--------------------|----------------------------------|------------------|--------------------|

| T1.1 $x = 1$       | T2.1 y = 0         | T2.1 y = 6                       | T1 Wx            |                    |

| T2.1 y = 0         | T1.1 $x = 1$       | 12.1 y = 0<br>T1.1 y = 1         | T2 Wy            | T1.1 $x = 1$       |

| T1.2 y = 1         | T1.2 y = 1         | T1.1 $y = 1$<br>T2.2 if (y == 1) | T1 Wy            | T1.2 y = 1         |

| T2.2 if $(y == 1)$ | T2.2 if $(y == 1)$ | (* /                             | T2 Ry            | T2.1 y = 0         |

| T2.3 $x = -1$      | T2.3, x = -1       | $T_{2.3,x} = -1$                 | T2 Wx            | T2.2 if $(y == 1)$ |

| T1.3 if(x $< 0$ )  | T1.3 if(x $< 0$ )  | T1.3 if( $x < 0$ )<br>T1.4,ERROR | T3 Rx            |                    |

| T1.4 ERROR         | T1.4,ERROR         | 11.4,EnnOn                       | T1 ERROR         |                    |

| ERROR              | ERROR              | ERROR                            | ERROR            | -                  |

Figure 2.1: Level of determinism, provided in record and replay systems

#### 2.4.3.1 Value Determinism

One of the strongest types of determinism that could be provided by record and replay systems is value determinism, which guarantees that all the read and write operations will happen with the same values, including so-called "blind" writes, which are not followed by corresponding read operations. This approach guarantees that output-visible and output-invisible events will appear in the secondary execution (Altekar and Stoica 2009). Its main drawback is extensive trace files. With a purpose to mitigate log sizes can be provided in relaxed form where either less events are being logged (Park, Zhou, Xiong, Yin, Kaushik, Lee, and Lu 2009) or the execution order of only write operations is being traced (Zhou, Xiao, and Zhang 2012), however, with a price of difficulties in replay phase.

## 2.4.3.2 Output Determinism

Output determinism states that the replay run outputs the same values as the original run (Altekar and Stoica 2009). It provides us with assurance of replay of output-visible events and faults such as crashes, core dumps, file corruptions, assertion violations. However, this type of determinism is considered weaker as it provides no guarantees regarding non-output properties of the original execution. Also, it does not guarantee that read and write operations happened in the same order as in original run. Depending on purposes of developer, replay can be relaxed by lowering of granularity of output events, for example on debug we might concentrate on failure events ignoring the exactness of value output and so on.

### 2.4.3.3 Path Determinism

This approach does not record values of operations but instead an execution path of each thread, aiming to repeat it on replay. Losing guarantees to replay the bug, it is still used to obtain in order to obtain symbolic execution of the program (Huang, Zhang, and Dolby 2013).

#### 2.4.4 Other choice criteria

- **Range in Time:** indicates whether the system requires the replay start point to be predetermined (*static time range*) or if it may be changed (*dynamic time range*). Systems with static time range usually rely on checkpoints, whereas systems with dynamic time range allow to replay an execution backwards.

- Multiprocessor and Data Race support: in a single-processor system, it suffices to record the synchronization order and the thread scheduling decisions to deterministically replay any concurrent program (Ronsse and De Bosschere 1999). In these systems, parallelism is actually an abstraction: only one thread physically executes and accesses memory at

a given point in time. However, in a multi-processor environment (SMP and multicores), providing deterministic replay becomes much more challenging. As threads do actually execute simultaneously on different processors, logging the thread scheduling in each processor is no longer enough to know the exact access ordering to shared memory locations. A way to address this issue is to capture the full thread schedule, which is not easy to do to efficiently. This is also the reason why replaying data races is a major challenge for multi-processor deterministic replay systems.

**Immediate Replay:** this criterion indicates whether a system is able to replay an execution at the first attempt or not. For instance, it is common for search-based systems to relax immediate replay guarantees in order to reduce the recording overhead.

# 2.5 Example Systems

In this section, we provide an overview of some of the most relevant record and replay systems representing the design choices previously described. To facilitate the comparison among the systems, we present an overall view on all the systems in the Table 2.2.

## 2.5.1 Hardware-Only Systems

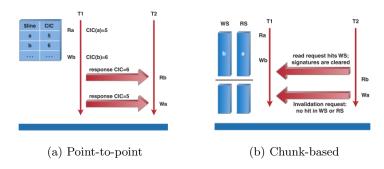

Many of the early record and replay systems have been designed considering the use of hardware support to detect data races, often piggybacking on the cache coherence protocol. For instance, Bacon and Goldstein (Bacon and Goldstein 1991) used a snooping bus to record all cache coherence traffic. In general, there are two main approaches to capture the information in hardware-only systems:

- *Data-driven:* Memory is logically divided into blocks (that consist of one or multiple memory words) and a timestamp is associated with each block. Every time a processor accesses a block, the timestamp is recorded and updated. This approach is also called point-to-point and FDR(Xu, Bodik, and Hill 2003) is the state of the art system, operating in this way.

- *Path-driven:* The log identifies sequences of data accesses that have been executed without interference from other threads. Each entry in the log, also called a *chunk*, stores the

#### 2.5. EXAMPLE SYSTEMS

address of all words that have been accessed in the sequence. Because of chunk division, this approach is also called chunk-based. For conciseness, the set of identifiers that are part of the chunk is stored as a *Bloom Filter* (Pokam, Pereira, Danne, Yang, King, and Torrellas 2009). Data accesses are added to the current chunk until a conflict exists. At that point, the chunk is recorded and a new chunk is initiated.

The major advantage of hardware-only systems is that they allow to achieve deterministic replay with little runtime overhead. Unfortunately, they are impractical in general due to the significant cost and amount of hardware modifications they require. Also, in many cases, one is not interested in logging the entire program but only parts of it. However, supporting selective logging would require even more changes to the hardware.

We briefly summarize some of the most relevant hardware systems in the next paragraphs:

### 2.5.1.1 FlightDataRecorder

FlightDataRecorder (Xu, Bodik, and Hill 2003), whose name is inspired in the mechanisms used in avionics to trace flight data, is a system designed to continuously log data about a program's execution with the goal of supporting the replay of the last second of a (crashed) execution. Since the system traces a substantial amount of information, the state of the application is periodically check-pointed, such that the log only needs to preserve the data accesses after the last checkpoint. FDR leverages on previous work for implementing the check-pointing operation, namely on the SafetyNet mechanism (Sorin, Martin, Hill, and Wood 2002). After a checkpoint, FDR logs access the cache. For this purpose, the system maintains an *instruction* counter (IC) for each core and a cache instruction count (CIC) field for each cache line; the CIC stores the IC of last instruction that accessed the cache line (Pokam, Pereira, Danne, Yang, King, and Torrellas 2009). FDR implements a number of optimizations (Netzer 1993) to avoid storing information that can be inferred from previous entries. Thus, on the left side of Figure 2.2 only dependency from T1-Wb to T2-Rb is logged, as T1-Ra to T2-Wa is consequentially implied by T1-Wb to T2-Rb. With these optimizations, the authors claim that FDR can induce less than a 2% slowdown in the execution of a program. In terms of space overhead, FDR produces logs of 35 MB in an interval of 1,33s. For a longer period, such as 3 hours of replay, the size of the log would amount to 320 GB.

#### 2.5.1.2 ReRun

ReRun (Hower and Hill 2008) is a path-driven approach, that identifies and logs sequences of data accesses that do not conflict with other threads. Such sequences, called *episodes*, are stored in a compressed format (using bloom filters as described before) along with a timestamp that identifies the order of the episode with regard to other episodes. Similar to point-to-point approach in FDR(Xu, Bodik, and Hill 2003), chunk-based approaches can also use transitive reduction to create smaller traces. As shown on the right side of Figure 2.2, the remote read T2-Rb conflicts with the write signature of T1 and causes T1 to end its chunk and to clear its signatures. Consequently, the request T2-Wa does not conflict and the dependency T1-Ra to T2-Wa is implied. In contrast to point-to-point approaches in which a timestamp is stored with each memory block, chunk-based approaches only need to store a timestamp per core to order chunks between threads. The bloom filter that encodes the data accesses during the episode, denoted *episode signature*, is used to detect conflicts among episodes. A conflict exists when one episode tries to access a data item that has been accessed by another episode. ReRun uses Lamport Clocks as timestamps for episodes, i.e., each core keeps a logical clock that is updated, according to Lamport's rules, to keep track of causal dependencies between reads and writes. During replay, episodes are executed according to the order of their timestamps. Although ReRun aimed at reducing the size of logs (when compared to FDR), it requires logical clocks to be piggybacked with every cache coherence operation, which is an additional source of overhead. In particular, the authors claim that ReRun's overhead is approximately 10%.

## 2.5.1.3 DeLorean

DeLorean (Montesinos, Ceze, and Torrellas 2008) is another path-driven hardware system for deterministic replay. As ReRun(Hower and Hill 2008), DeLorean also logs chunks using signatures, but in a different way: in DeLorean's multi-processor execution environment, cores are continuously executing chunks that are separated by register checkpoints. To detect a conflict, the system compares chunks' signatures. However, the updates of a chunk can only be seen after chunk commits. If a conflict is found, the chunk is squashed and re-executed. As with ReRun, replay determinism is achieved by replaying chunks according to their timestamp order.

Figure 2.2: Hardware-only techniques (Source: Intel Corporation, 2009)

## 2.5.2 Hybrid Systems

Hybrid systems combine hardware and software support for record and replay. They aim at supporting a wider range of scenarios while reducing the costs associated with building dedicated hardware. In the following paragraph, we refer to one such system.

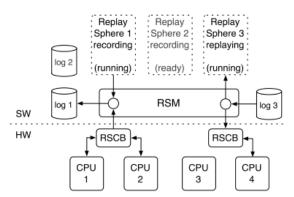

#### 2.5.2.1 Capo

Capo (Montesinos, Hicks, King, and Torrellas 2009) uses hardware support to record the interleaving of threads and software support to trace other sources of non-determinism. It also provides support for logging only a subset of the entire program (for instance, the user code but not the operating system code). This is achieved by defining an abstraction named *Replay Sphere*, that encapsulates the set of threads whose operation need to be logged, and by defining the explicit and implicit transitions that allow the core to enter and leave the replay sphere. This system's concept can be better understood with Figure 2.3, which depict logical representation of system. Here, SW - software, HW - hardware, RSM - Replay Sphere Manager, RSCB - Replay Sphere Control Block, CPU - Central Processing Unit. Capo generates a combined log of 2.5 bits to 3.8 bits per kilo-instruction of the program, which results in a slowdown of the system execution on the order of 21% to 41%.

## 2.5.3 Software-Only Systems

There is a great variety of software-only techniques that provide record and replay. In the following, we briefly describe some of the most relevant software-based solutions proposed over

Figure 2.3: Logical representation of Capo

the years. For better understanding, we present an example on Figure 3.2 with the log structure of all the systems, listed in Table 2.1

## 2.5.3.1 Instant Replay

Instant Replay (LeBlanc and Mellor-Crummey 1987a) can be considered a pioneer softwareonly record and replay system. It follows an order-based approach: the system records the history of accesses to all the shared objects with respect to a particular thread. As this requires to uniquely identify shared objects dynamically, each object is extended with a custom version number that gets incremented after every write access during both record and replay. The computation model of Instant Replay is based on the CREW (Concurrent-Reader-Exclusive-Writer) protocol, which assigns two possible states to each shared object:

- *Concurrent Read*: implies a state where no processor is allowed to write, but all processors are allowed to read the value with no restrictions.

- *Exclusive Write*: implies a state where only one processor (called the *owner*) is allowed to read and write, and other processors are deprived of access.

This method makes the record phase quite costly and, due to the small granularity of shared memory accesses, tends to create enormous trace files. It has been reported that performance suffers an overhead up to 10x times of original execution time.

#### 2.5.3.2 DeJavu

DeJavu (Choi and Srinivasan 1998) is another order-based system, designed at IBM ten years after Instant Replay, with the purpose of providing deterministic replay for Java programs. This system is based on capturing the total order of thread accesses, thus allowing to deterministically replay non-deterministic executions. To this end, DejaVu uses a global timestamping scheme, which exists in two categories:

- *Critical events*, which encompass synchronization points and shared memory accesses, relevant to the record and replay process.

- *Non-critical events*, which are those that only influence the thread where they get executed, so their scheduling is not utterly relevant.

This approach becomes less appealing when the number of threads and cores of a processor increases, as the overhead to capture the global order of all thread events becomes extremely high.

#### 2.5.3.3 RecPlay

RecPlay (Ronsse and De Bosschere 1999) is a successor of DejaVu, but, unlike the latter, uses Lamport clocks instead of a global clock. RecPlay is based on the assumption that most programs do not have data races, and that the synchronization races are intentional and beneficial. As such, this solution traces thread accesses only to synchronization variables (such as monitoring of entries and exits). Since these Lamport timestamps are stored in the trace in a compressed from, the runtime slowdown is not very large. In the replay phase, the trace is consulted for every synchronization operation(Ronsse, Christiaens, and De Bosschere 2001). The drawback of this approach is the loss of determinism (as many shared memory accesses may not be synchronized) and the impossibility to replay problematic runs in the presence of data races(Ronsse, De Bosschere, Christiaens, de Kergommeaux, and Kranzlmüller 2003).

#### 2.5.3.4 JaRec

JaRec (Georges, Christiaens, Ronsse, and De Bosschere 2004) is a portable record and replay system, designed especially for Java applications. This system operates at the bytecode level. Its working principle is very similar to RecPlay (Ronsse and De Bosschere 1999), as it is also based on assumption that applications are data-race free. In particular, JaRec tracks only the lock acquisition, thus it is not able to reproduce buggy execution caused by data races as well. In other words, this system provides deterministic replay, but only until the first data race condition. This proviso makes JaRec and its predecessor RecPlay (Ronsse and De Bosschere 1999) unattractive in practice. In terms of performance degradation, JaRec's recording overhead lies between 10% to 125%, depending on the scale of the benchmark used.

#### 2.5.3.5 iDNA

iDNA (Bhansali, Chen, De Jong, Edwards, Murray, Drinić, Mihočka, and Chau 2006) is an instruction level tracing framework, based on dynamic binary instrumentation. This system addresses non-determinism by tracking and restoring changes to registers and main memory. In order to do so, it maintains a copy of the user-level memory, which is implemented as a direct mapped cache. iDNA monitors the data values at every dynamic instance of instructions during the execution, and tracks the order of synchronization operations, which means that it does not support the reproduction of data races. An interesting feature of iDNA is the possibility to replay threads independently, as each of them maintains its own copy. But this can also be seen as a source of large log files. In fact, iDNA produces, on average, dozens of mega-bytes per second of trace sizes and incurs runtime overhead of 11x.

### 2.5.3.6 LEAP

LEAP (Huang, Liu, and Zhang 2010) is a deterministic replay solution for concurrent Java programs on multi-processors. LEAP is based on the observation that there is no need to track the global ordering of thread accesses to shared memory locations. Instead, it suffices for each shared variable to track only the thread interleaving that it sees (denoted *access vector*). Therefore, this solution produces a set of vectors containing the local access order with respect to the shared memory locations, rather than a single vector with the global order. As each shared variable has its own synchronization, this approach allows accesses to different variables to be recorded in parallel, thus imposing lower runtime overhead. Despite providing slightly weaker determinism guarantees, the authors prove that LEAP's technique does not affect the correctness of the replay. One of the limitations of LEAP is that it does not distinguish between

#### 2.5. EXAMPLE SYSTEMS

different instances of the same class, which creates false dependencies between different objects and a consequent increase in the recording overhead. Nevertheless, the experimental evaluation in (Huang, Liu, and Zhang 2010) showed that LEAP is up to 10x times faster than global order approaches (e.g. Instant Replay (LeBlanc and Mellor-Crummey 1987a) and DejaVu (Choi and Srinivasan 1998)) and 2x to 10x faster than JaRec (Georges, Christiaens, Ronsse, and De Bosschere 2004), albeit it still incurs huge overhead for applications with many shared accesses. As for space efficiency, trace sizes range from 51 to 37760 KB/sec.

#### 2.5.3.7 ORDER

ORDER (Yang, Yang, Xu, Chen, and Zang 2011) was developed in order to record and reproduce non-deterministic events inside the Java virtual machine (JVM). This system follows an order-based approach and is based on two main observations: i) good locality at the object level with respect to thread accesses, and ii) frequent object movements due to garbage collection. ORDER literally records the order of threads accessing shared objects, eliminating unnecessary dependencies introduced by moving objects within memory during garbage collection. It also implements an offline log compression algorithm, used to filter out remaining unnecessary dependencies from thread-local and assigned-once objects, caused by imprecise static compiler analysis. To this end, ORDER extends the header of each object with following five meta-data fields:

- Object Identifier (OI) that works as an unique hash of the object.

- Accessing thread identifier (AT) and access counter (AC), which are used to maintain the current status of the object's access time-line. Every time-line recorded by ORDER can thus be interpreted as "the object OI is accessed by thread AT for AC times".

- *Object-level lock* that is used to protect the whole object and synchronize the recording of the accesses to it.

- *Read-Write flag*, which records whether the current time-line record is read-only or readwrite, for future log compression.

In both record and replay phases, ORDER relies on instrumentation actions added to the JVM. At *record* time, the system compares the AT in the object header with the identifier of the current accessing thread (CTID). If the access belongs to the same thread, ORDER increments the corresponding AC. Otherwise, ORDER appends the tuple (AT, AC) to the log and proceeds with the execution. During *replay*, the process is similar: the system checks if AT == CTID and if the requesting thread is the expected one (according to the log), it decrements the AC allowing the thread to continue executing. Otherwise, the thread gets blocked until its turn. Performance evaluation results show that ORDER is 1.4x to 3.2x faster than LEAP.

## 2.5.3.8 CARE

CARE (Jiang, Gu, Xu, Ma, and Lu 2014) is a very recent application-level deterministic record and replay technique for Java concurrent programs. CARE employs an order-based approach that leverages thread locality of variable accesses in order to avoid recording all read-write linkages. Concretely, during the record phase, CARE assigns each thread with a software *cache*. This cache is updated every time the thread reads or writes on a shared variable, and is queried whenever the thread performs a read operation. Write operations are always synchronized and recorded into the trace file whenever a new thread writes on a given shared variable, whereas read operations are only logged in the presence of a *cache miss*. A cache miss occurs when the value read from the shared variable differs from the one previously buffered in the cache, meaning that another thread must have written on this variable before. At this point, CARE logs the exact read-write linkage by redoing the read action again with synchronization.

In the replay phase, CARE does not try to determine all non-recorded read-write linkages. Instead, it simulates the behavior of all caches and overrides read values from memory by values buffered in thread-local caches. This provides value-determinism guarantees at replay. Evaluation shows that CARE resolved all missed linkages for sequentially consistent replay, and exhibited 3.4x reduction on runtime overhead and 7x reduction on log size when compared to LEAP.

All the aforementioned systems employ an order-based approach. In the following, we describe some of most relevant search-based solutions.

#### 2.5.3.9 PRES