# Integrating Transactional Memory Support in the TensorFlow Framework

Facoltà di Ingegneria dell'Informazione, Informatica e Statistica Master of Science in Engineering in Computer Science

Candidate Davide Leoni ID number 1614811

Thesis Advisor Prof. Bruno Ciciani Co-Advisors

Prof. Francesco Quaglia Prof. Paolo Romano Prof. Bruno Martins Manuel Barreto Lima Reis

Academic Year 2016/2017

**Integrating Transactional Memory Support in the TensorFlow Framework** Master thesis. Sapienza – University of Rome

@ 2017 Davide Leoni. All rights reserved

This thesis has been types et by  $\ensuremath{\mathrm{L}^{\!\!A}\!T_{\!\!E}\!X}$  and the Sapthesis class.

Author's email: davide.leoni90@gmail.com

#### Acknowledgments

The thesis work described in this document was conducted from May to September 2017 at the Instituto de Engenharia de Sistemas e Computadores, Investigação e Desenvolvimento em Lisboa (INESC-ID)<sup>1</sup> within the SATURN<sup>2</sup> (Spatio-temporal cloud store for big-data applications) project. The work was done together with Manuel Barreto Lima Reis (who is currently pursuing a PhD degree in Computer Science) and was supervised by Prof. Paolo Romano, from Instituto Superior Técnico of the University of Lisbon, Prof. Bruno Emanuel da Graça Martins, from the same institute, and Prof. Francesco Quaglia, from Università degli Studi di Roma Tor Vergata. I want to thank all of them: collaborating with them was a pleasure and allowed me to improve much my technical preparation. I am really grateful to Paolo and Francesco, as they gave me the opportunity of working on a very interesting project, in a stimulating international environment. I enjoyed much my time in Lisbon, in particular at the INESC-ID institute, and I learned a lot, both from the professional and the personal point of view. I must acknowledge all the colleagues from the institute, who offered me a great support: Daniel Castro, Pedro Raminhas and Shady Alaa Issa. My sincere appreciation also goes to Bruno, for his contribution and for the time he dedicated to me. A special thank goes to my friend Manuel, for his fundamental help and for all the good moments spent together. Last, but not least, I must thank my advisor, for his availability and support.

<sup>&</sup>lt;sup>1</sup>www.inesc-id.pt <sup>2</sup>www.gsd.inesc-id.pt/blog/saturn

### Contents

| 1        | Intr | oduct   | ion 1                                                                                                                              |

|----------|------|---------|------------------------------------------------------------------------------------------------------------------------------------|

|          | 1.1  | Motiv   | ations                                                                                                                             |

|          | 1.2  | Goal    |                                                                                                                                    |

| <b>2</b> | Bac  | kgrou   | nd 3                                                                                                                               |

|          | 2.1  | Transa  | actional Memories $\ldots \ldots \ldots \ldots \ldots \ldots \ldots \ldots \ldots 3$                                               |

|          |      | 2.1.1   | Introduction                                                                                                                       |

|          |      | 2.1.2   | $Implementation \dots \dots$ |

|          |      | 2.1.3   | Software Transactional Memories                                                                                                    |

|          |      | 2.1.4   | Hardware Transactional Memories                                                                                                    |

|          |      | 2.1.5   | POWER8                                                                                                                             |

|          |      | 2.1.6   | Intel Haswell                                                                                                                      |

|          | 2.2  | Transa  | actional Lock Elision                                                                                                              |

|          |      | 2.2.1   | Intel Transactional Synchronization Extensions                                                                                     |

|          |      | 2.2.2   | POWER ISA Transactional Memory Support 13                                                                                          |

|          |      | 2.2.3   | GCC Transactional Memory Interface                                                                                                 |

|          | 2.3  | Tenso   | rFlow                                                                                                                              |

|          |      | 2.3.1   | Introduction                                                                                                                       |

|          |      | 2.3.2   | Building the Dataflow Graph                                                                                                        |

|          |      | 2.3.3   | Executing the Dataflow Graph 19                                                                                                    |

|          |      | 2.3.4   | Visualizing the Dataflow Graph                                                                                                     |

|          |      | 2.3.5   | Architecture                                                                                                                       |

|          | 2.4  | Statis  | tical Learning                                                                                                                     |

|          |      | 2.4.1   | Overview                                                                                                                           |

|          |      | 2.4.2   | Linear Regression                                                                                                                  |

|          |      | 2.4.3   | Logistic Regression                                                                                                                |

|          |      | 2.4.4   | Gradient Descent                                                                                                                   |

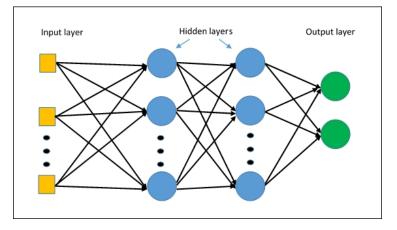

|          | 2.5  | Artific | cial Neural Networks                                                                                                               |

|          |      | 2.5.1   | Perceptrons                                                                                                                        |

|          |      | 2.5.2   | Training Perceptrons                                                                                                               |

|          |      | 2.5.3   | Multilayer Perceptrons                                                                                                             |

|          |      | 2.5.4   | Variations to the Gradient Descent Algorithm                                                                                       |

|          |      | 2.5.5   | Convolutional Neural Networks                                                                                                      |

$\mathbf{v}$

| 3        | Inte           | grating Transactional Memories in TensorFlow                        | 35        |

|----------|----------------|---------------------------------------------------------------------|-----------|

|          | 3.1            | Parallel Gradient Descent                                           | 36        |

|          | 3.2            | Gradient Descent in the TensorFlow                                  | 37        |

|          |                | 3.2.1 Python API                                                    | 37        |

|          |                | 3.2.2 Back-end Implementation                                       | 38        |

|          | 3.3            | Transactional Application of the Gradient Descent                   | 39        |

|          |                | 3.3.1 Lock Elision with Hardware Transactional Memory               | 39        |

|          |                | 3.3.2 Application of the Updates with Software Transactional Memory | 42        |

|          | 3.4            | Eliding All the Locks in TensorFlow                                 | 43        |

| <b>4</b> | $\mathbf{Exp}$ | eriments and Results                                                | <b>45</b> |

|          | 4.1            | The MNIST dataset                                                   | 46        |

|          | 4.2            | Training of the Models                                              | 46        |

|          | 4.3            | Evaluation of the Models                                            | 47        |

|          | 4.4            | MNIST Softmax Regression (mnist_softmax)                            | 48        |

|          | 4.5            | MNIST Convolutional Network(mnist_deep)                             | 49        |

|          | 4.6            | TLE of the Lock for the Application of the Updates                  | 50        |

|          |                | 4.6.1 Elision with HTM                                              | 50        |

|          |                | 4.6.2 Elision with STM                                              | 56        |

|          | 4.7            | Global TLE                                                          | 58        |

| <b>5</b> | Con            | clusions                                                            | 67        |

## List of Figures

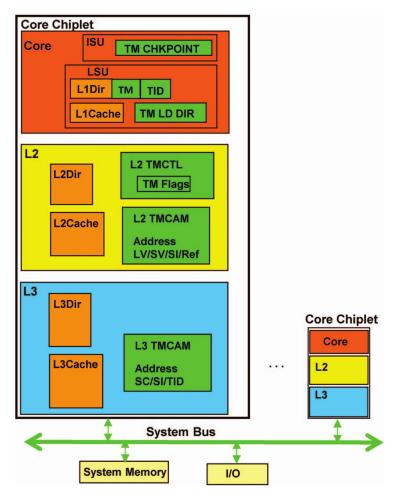

| 2.1  | The HTM architecture on POWER8                                                              | 10 |

|------|---------------------------------------------------------------------------------------------|----|

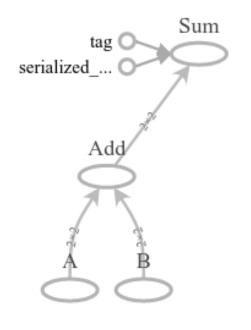

| 2.2  | Dataflow graph relative to Listing 2.9                                                      | 22 |

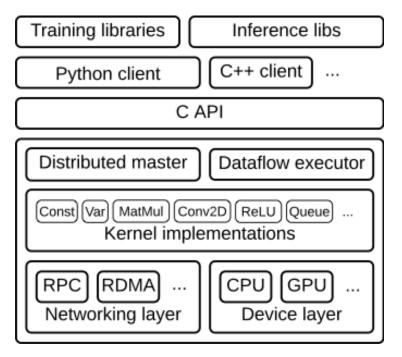

| 2.3  | Architecture of TensorFlow                                                                  | 23 |

| 2.4  | Multilayer perceptron                                                                       | 31 |

| 3.1  | The gradients in TensorBoard                                                                | 37 |

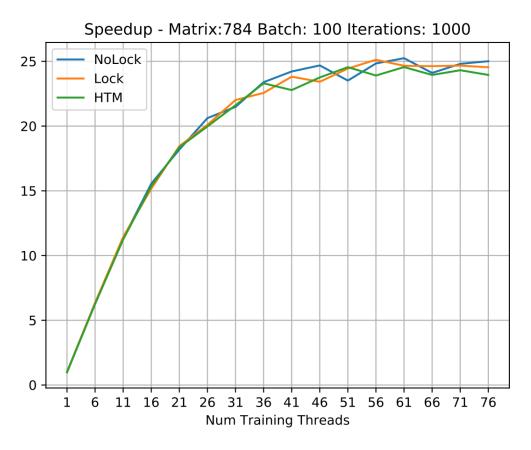

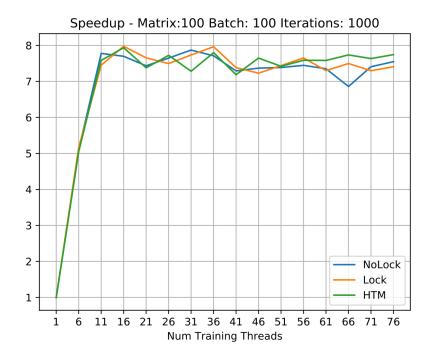

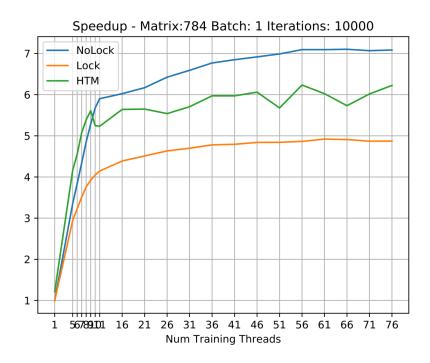

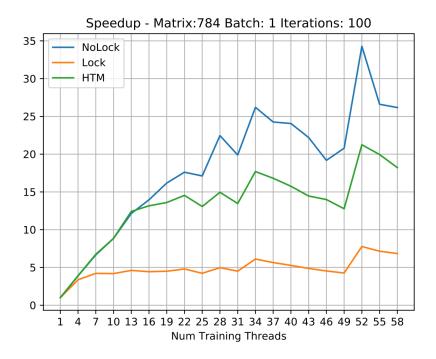

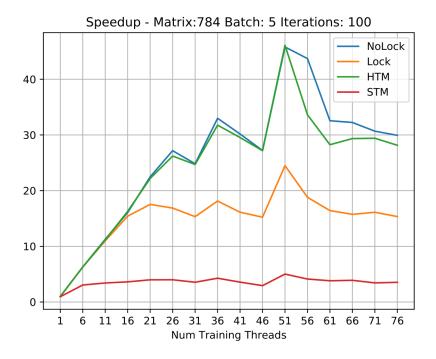

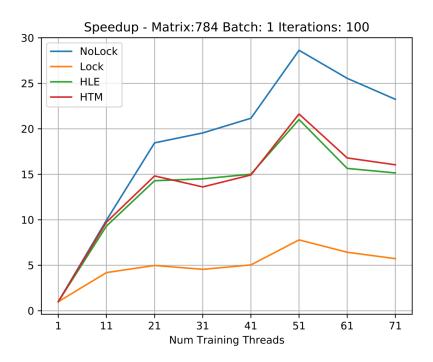

| 4.1  | Speedup with HTM elision on Intel TSX - mnist_softmax - size:784                            | 53 |

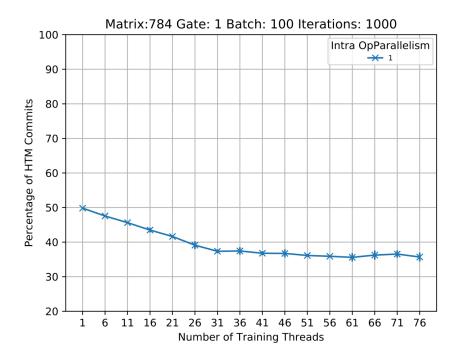

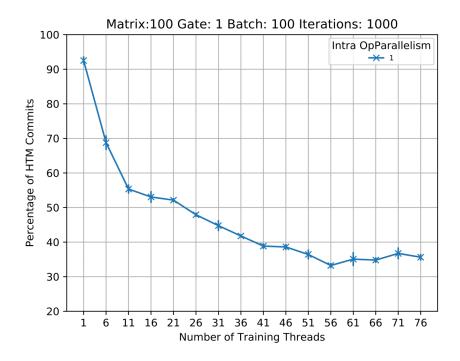

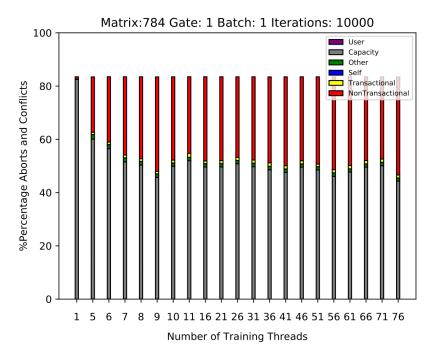

| 4.2  | Commits with HTM elision on Intel TSX - mnist_softmax - size:784                            | 54 |

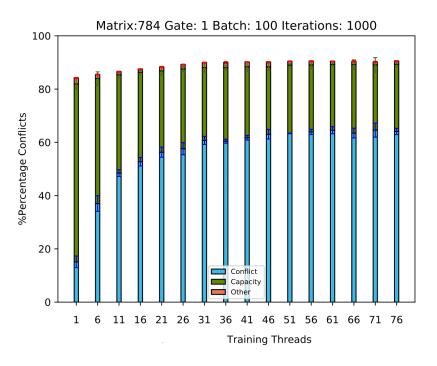

| 4.3  | Conflicts with HTM elision on Intel TSX - mnist_softmax - size:784                          | 55 |

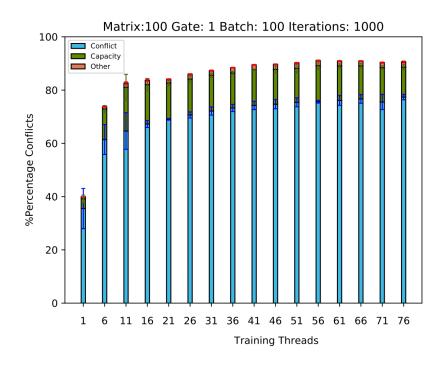

| 4.4  | Conflicts with HTM elision on Intel TSX - mnist_softmax - size:100                          | 56 |

| 4.5  | Commits with HTM elision on Intel TSX - mnist_softmax - size:100                            | 57 |

| 4.6  | Speedup with HTM elision on Intel TSX - mnist_softmax - size:100                            | 58 |

| 4.7  | Speedup with HTM elision on POWER ISA - $\texttt{mnist\_softmax}$ - $\texttt{size:}784$     | 59 |

| 4.8  | Failures with HTM elision on POWER ISA - $\texttt{mnist\_softmax}$ - $\texttt{size:}784$    | 60 |

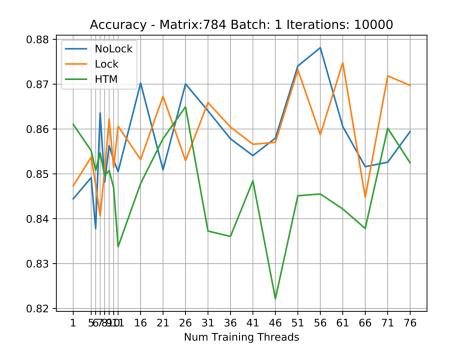

| 4.9  | Accuracy with HTM elision on POWER ISA - <code>mnist_softmax</code> - <code>size:784</code> | 60 |

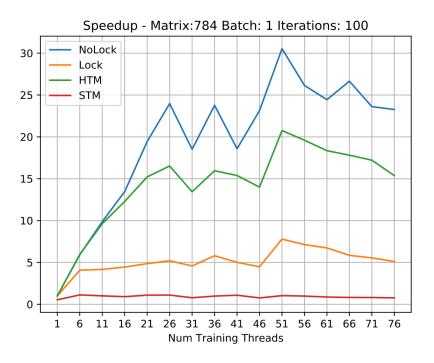

| 4.10 | Speedup with HTM elision on Intel TSX - mnist_deep - size:784,                              |    |

|      | batch:1                                                                                     | 61 |

| 4.11 | Speedup with HTM elision on Intel TSX - mnist_deep - size:784,                              |    |

|      | batch:15                                                                                    | 61 |

| 4.12 | Accuracy with HTM elision on Intel TSX - mnist_deep - size:784,                             |    |

|      | batch:1                                                                                     | 62 |

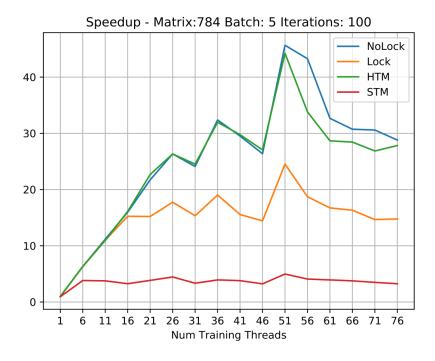

| 4.13 | Speedup with STM - default c.m., size:784, batch:1                                          | 62 |

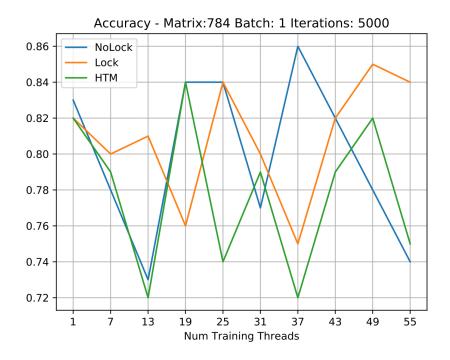

| 4.14 | Speedup with STM - default c.m., size:784, batch:5                                          | 63 |

| 4.15 | Speedup with STM - backoff c.m., size:784, batch:1                                          | 63 |

| 4.16 | Speedup with STM - backoff c.m., size:784, batch:5                                          | 64 |

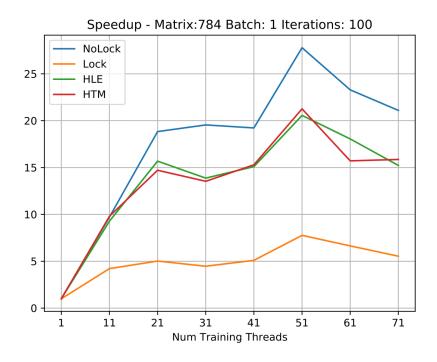

| 4.17 | Speedup with Global TLE - default elision configuration                                     | 64 |

| 4.18 | Speedup with Global TLE - custom elision configuration                                      | 65 |

|      |                                                                                             |    |

### Listings

| 2.1 | Locks vs. Transactions                                 | 4  |

|-----|--------------------------------------------------------|----|

| 2.2 | Transactional Lock Elision with TSX                    | 13 |

| 2.3 | Transactional Lock Elision with POWER ISA              | 14 |

| 2.4 | Low-level HTM GCC built-in functions on POWER ISA      | 15 |

| 2.5 | Transactional code using $libitm$                      | 16 |

| 2.6 | Transactional code using the GCC RTM interface         | 17 |

| 2.7 | Start transaction with HLE                             | 17 |

| 2.8 | End transaction with HLE                               | 18 |

| 2.9 | Add matrices in TensorFlow                             | 20 |

| 3.1 | Train a linear model                                   | 38 |

| 3.2 | Original application of the updates, with Eigen        | 39 |

| 3.3 | HTM-friendly application of the updates, without Eigen | 39 |

| 3.4 | HTM elision on Intel TSX                               | 40 |

| 3.5 | HTM elision on POWER ISA                               | 41 |

| 3.6 | GCC TM application of the updates                      | 43 |

| 4.1 | Load MNIST in Python                                   | 46 |

### Chapter 1

### Introduction

#### **1.1** Motivations

It only takes to look in any academic search engine at the number of publications related to it, to realise how *machine learning* has been having a growing momentum in the last decades. Nowadays, the core business of the main world-wide leading companies, like Facebook, Google or Amazon, is largely based on the capacity of training models. This is particularly true for one of the branches of machine learning, *deep learning*, whose success has been impressively increasing in the very last few years at a large scale. Such a popularity is understandable considering the great progresses made in various areas (for example computer vision, natural language processing, speech recognition and information retrieval) thanks to the algorithms provided by this research field [1, 11, 27].

Hence it does not come as a surprise to know that many frameworks and libraries, both open and closed source, exist to implement and experiment with these algorithms. Nevertheless, although machine learning, and even more deep learning, have been only recently catching the attention of the researchers, it is been now many years since the first libraries and frameworks for machine learning have been introduced. A list of the most famous ones can include, in chronological order, the OpenCV library for C++, the *scikit-learn* library for Python, and the *Apache Hadoop* platform for Java. Focusing on deep learning, the oldest example, *Torch*, dates back to 2002 and was then followed by *Theano* and *Caffe*.

In November 2015, Google released *TensorFlow* (TF), a software library for the implementation and training of machine learning models. After the very first releases, whose performances were poor compared to the other libraries [4], TF rapidly gained a broad consensus among developers (as witnessed by the thousands of projects on GitHub making use of it) and researchers. This is probably due to one characteristic that makes TF unique compared to its competitors: flexibility [27]. As a matter of fact, TF supports *distributed execution* across various kinds of devices, with very different computational power, from mobile phones to GPUs. Such an heterogeneity of hardware platforms reflects into a variety of tasks and goals, which range from large-scale training with many dedicated machines in a production environment, to experimenting new algorithms on simple smartphones. Overall, on one hand, the objective pursued by TF is to make machine learning and deep learning accessible

to the broadest audience as possible; on the other hand, it puts a strong accent on the adoption of parallel and distributed computing to make machine learning faster [1, 2, 27]. Indeed, in the last decade the rapid spread of low-cost machines with multiple cores has made possible to apply machine learning to datasets much larger than before, allowing to improve the accuracy of trained models [6, 23]. Nevertheless, because of the synchronization primitives that have to be used when the training is performed in parallel, the scalability is still limited.

#### 1.2 Goal

The great popularity of TF, together with the current emphasis on training models in parallel, suggested the idea of investigating the benefits of providing this framework with the support for *transactional memories*. These, indeed, removing the need for the classic synchronization primitives (more on this in Section 2.1), can help to improve the scalability of programs run on multiple processors. As a consequence, the algorithms provided by TF, when applied in the context of large-scale training, could potentially profit from the application of transactional memories. The intended goal of this thesis consisted in verifying whether this speculation was true.

## Chapter 2 Background

This chapter contains an overview of the fundamental concepts which this dissertation is based on. The first part deals with the transactional memories, starting from the reasons that motivated their introduction, describing the general design concepts and bringing some concrete examples. The following section is dedicated to TensorFlow, the library for machine learning by Google, at the center of this thesis work. Considering its complexity, and the high number of functionalities, it is not trivial (and out of scope) to provide a complete description of the framework. The attention is thus focused on the aspects that are most relevant in the perspective of integration the transactional memory support. The last section provides a theoretical background related to the machine learning models taken into account as testbeds for the experiments reported in this work.

#### 2.1 Transactional Memories

#### 2.1.1 Introduction

After many years since the first parallel architectures came to light, it is now clear that writing programs that exploit effectively all their computational power is not a trivial task [14]. Indeed, the well-known synchronization primitives (locks, mutexes, semaphores, etc.), required to coordinate the action of threads (or processes) on shared data, introduce some complications. On one hand, it is necessary to keep as tiny as possible the *critical sections*, the piece of code protected by the primitives, in order to provide scalability. On the other hand, the finer the grain of the critical sections, the more complicated and the trickier to debug is the associated code. Besides performances, when not properly used synchronization primitives can threat the progress of the programs (*deadlocks*) or their correctness (*race conditions*). Last, but not least, explicit synchronization is not composable. In alternative, programs designed to run in parallel can adopt *lock-free algorithms*, but it is even more difficult to design them and to prove their correctness, so they are actually used for very specific domains.

Given all these issues, *Transactional memories* were introduced to provide programmers with a new abstraction that made parallel programming easier. The idea was borrowed from the world of databases, which are able to run queries simultaneously on multiple processors without the programmer to be concerned about the concurrency of the execution: this is achieved wrapping the computation with *transactions*. In databases, transactions are the fundamental unit of execution: they are a set of instructions that have to be executed sequentially. They have four basics characteristics:

- 1. *atomicity*: the effects of a transaction are made visible (the transaction is said to have *committed*) only if all the enclosed operations completed successfully. If any of these fails, the whole transaction is said to have *failed* and the system remains untouched as if the transaction had been never executed

- 2. *consistency*: the transaction must not alter the consistency properties of the database

- 3. *isolation*: each transaction must not interfere with other transactions (if any) executed simultaneously

- 4. *durability*: once a transaction has committed, its effects on the database are definitive

Each transaction is executed as if it the associated computation was the only one running in the system, despite multiple transactions can be executed simultaneously. The underlying implementation deals with the concurrency issues transparently to the programmer and still guarantees *serializability*: the net result of the simultaneous execution of the transactions is the same as if the transactions run sequentially, so the programmer is not worried by synchronization of the operations. Transactional memories are intended to provide the support for performing the concurrent read and write to shared memory addresses applying the semantics of the database transactions [14]. As a consequence, programmers are relieved from the burden of explicitly applying synchronization primitives, since the properties of the transactions offer the guarantees necessary to solve the synchronization problems. Developers only have to identify the code associated with a critical section and surround it with a transaction using an interface similar to the one shown below.

```

int balance;

lock protect balaance;

void deposit (int x) {

void deposit (int x) {

protect_balance.lock();

startTx();

balance += x;

balance += x;

protect balance.unlock();

endTx();

}

}

void withdraw (int x) {

void withdraw (int x) {

protect_balance.lock();

startTx();

balance -= x;

balance -= x;

protect_balance.unlock();

endTx();

}

}

```

Listing 2.1. Locks vs. Transactions

#### 2.1.2 Implementation

This section provides an overview of the underlying mechanisms of transactional memories, independently of their specific implementation. First of all, it is necessary to handle the concurrent access to shared data in order to achieve isolation between transactions. Two transactions are said to determine a *conflict* if they execute two conflicting operations (two writes or one read and one write) on the same memory addresses: not only have conflicts to be detected, but they also have to be resolved. Three types of approach are possible [14]:

- *pessimistic*: at the moment of executing each operation inside a transaction, it is checked whether it will not produce a conflict; if that is so, the system takes some actions to avoid it

- *optimistic*: transactions are executed until a conflict is detected at only at that the point, actions are taken to resolve the conflict, possibly aborting transactions

- *hybrid*: it is possible, for example, to apply the pessimistic control only to conflicts between write operations and use instead the optimistic control for read operations. Another possibility is to use optimistic control and define some *irrevocable transactions* which are guaranteed to complete

In case the optimistic concurrency control is chosen, a further design decision regards the granularity of the detection of a conflict: in *Software Transactional Memories* (see Section 2.1.3) the resolution of the detection corresponds to entire objects, while in *Hardware Transactional Memories* (see Section 2.1.4) corresponds to single lines of the cache. Another important aspect of the detection is the time when it occurs. There are three moments, in chronological order with respect to the execution of the transaction, when a conflict can be detected [14]:

- 1. before the transaction is actually started

- 2. during its execution, a transaction can check whether the data it has accessed have been modified by other concurrent transactions

- 3. at "commit-time', when the transaction has already concluded its work

Furthermore, in order to detect conflicts, some implementations monitor the intersection of the set of accessed addresses only between committed and on-going transactions, while others also consider the intersection between transactions that are not terminated yet. Finally, transactional memories are required to keep track of the effects produced by the operations they contain, in order for them to be removed should the transaction be aborted. As regards with this aspect, there are two alternatives [14]:

- 1. *direct update*: the write operations directly replace the content of memory addresses to which they are applied and the old content is stored in an *undo-log*: this will be consulted, in case of abort, to restore the state of the memory antecedent to the execution of the transaction

- 2. *deferred update*: the results of the write operations are written to a *redo-log* and if the transaction eventually commits they are propagated to the memory

#### 2.1.3 Software Transactional Memories

The idea behind *Software Transactional Memories* was inspired by the work presented in [28], which first introduced the concept of "transaction" outside the domain of databases. Anyway, the current implementations of STMs are quite different from the mechanism presented in that work, where a transaction was required to first declare the memory addresses it was about to work with [14]. Many examples of STMs exist nowadays and each represents a different approach in the implementation of some basic mechanisms necessary to build STMs.

One of these mechanisms regard the storage of the *metadata* necessary to keep track of the memory locations accessed by the transactions. Two alternatives are possible:

- 1. storing the metadata as part of the object allocated by the program (*object-based*)

- 2. creating a mapping from each memory location to the address where are stored the related metadata (*word-based*)

The first solution is more convenient in terms of time required to access the metadata, since they are tightly connected to the object they refer to; on the other hand, since the metadata are usually stored in the same cache line as the object, two concurrent accesses to different fields of the same object will be detected as a conflict by the cache coherency protocol. Undo-logs (see Section 2.1.2) are usually allocated using lists, while for redo-logs the implementation has to be more complex in order to avoid the degradation of performances. Unlike the undo-log, indeed, the redo-log has to be checked every time a transaction reads a memory location previously written by another transaction, so that the former can see the speculative updates performed by the latter. The computational complexity of searching for these updates in a list is linear, and this is not acceptable from the point of view of performances, so often a hash table is used instead. STMs also need to keep track of the memory locations a transaction read from (*read-set*) and of those it wrote to (*write-set*).

The STM implementation used in some of the experiments described in this dissertation is  $TinySTM^{-1}$  [9, 10], which inherits many of its mechanism from the TL2 algorithm [8]. This algorithm makes use of versioned locks to store the metadata relative to a memory location accessed by a transaction. Versioned locks combine a mutual exclusion lock, that has to be acquired by write operations, with a version number, incremented every time the lock is grabbed and then released. If the lock is free, no write operations is currently being performed and the version number reflects the current state of the object; otherwise, the version number refers to the transaction that is accessing the object the metadata is associated with. TL2 adopts deferred updates: the lock, that protects the critical section executed transactionally, is acquired only when the transaction is ready to commit. Moreover, TL2 relies on a *global clock*, namely a counter, unique for the whole application, incremented by one when a writing transaction commits. When a transaction starts, it reads the value of the global clock: this value is referred to as *read-version* to distinguish it from the *write-version*, which instead is the value of the global clock incremented by a transaction before committing. The version number of each object is equal to the

<sup>&</sup>lt;sup>1</sup>tmware.org/tinystm

write version of the last transaction that modified it and successfully committed. A read-only transaction works as follows:

- 1. gets a read-version, reading the global clock

- 2. speculatively performs load operations: before each load, checks whether the versioned-lock of the memory address is free and whether the version number is less than or equal to the read version. If either of the two checks fails, the transaction is aborted, because this means that a write transaction meanwhile committed and modified the value of the location

It has to be noted that read-only transactions have the great advantage of avoiding that a read-set gets built for them; moreover, the read-version ensures the consistency of the view of the memory of a transaction. Unsurprisingly, a write transaction is more complex:

- 1. gets a read-version, reading the global clock

- 2. speculatively performs load ans store operations, logging them respectively in a read-set and a write-set. The load instructions, before actually accessing the memory, first check if the address is contained in the write-set and, if so, the corresponding value is returned. Moreover, for each load is made the same double check as in read-only transaction: this ensures that a memory location has not been concurrently modified by another transaction.ì

- 3. when the transaction is ready to commit, it tries to acquire all the locks of the locations in the write-set: if only one of these is not successfully grabbed, the transaction aborts

- 4. the write version is obtained, reading the global clock after having incremented it

- 5. before committing, the read-set is further validated to guarantee that, during the preceding two steps, no modification has been made to the addresses read

- 6. commit: for all the locations in the write set, the new value is stored, the version number is initialized to the write-version and then the lock is released

The main advantages of implementing transactional memories in software rather than using hardware resources is that software in general is easier to adapt and to modify.

#### 2.1.4 Hardware Transactional Memories

Hardware Transactional Memories represent a step forward with respect to STMs under many points of view. From the performances point of view, for example, they have less overhead than STMs. Also they can be applied more transparently to existing environments and they allow to save energy compared to STMs. Analogously to STMs, various types of HTMs have been proposed, but it still possible to categorize them on the basis of some design choices. Firstly, as regards with the definition of the boundaries of a transaction, there are two types of HTMs:

- 1. *explicit HTMs* provide new sets of instructions to directly specify which load and store instructions have to be performed inside a transaction; examples are [15, 30]

- 2. *implicit HTMs* only allow to specify where a transaction starts and where it finishes, treating all the memory accesses in between as part of the transaction; [25] and [7] belong to this group

HTMs usually exploit the hardware cache to store the *read set* (set of memory addresses read by a transaction) and the *write set* (set of memory addresses modified by a transaction). For the read set this is as simple as setting an extra "read bit" in the cache line containing the address accessed by a transaction. As for the write set, this is not so easy to deal with, since some cache coherency protocols allow that a modification to an address is first written in the cache and then propagated to the main memory. An alternative approach consists in allocating dedicated extra spaces for the read and write sets. Nevertheless, the usage of the hardware cache has a further advantage: it allows to rely on the *cache coherency protocols* for the detection of conflicts. As a matter of fact, the most common of this protocols, M.O.E.S.I defines five states for a cache line (modified, owned, exclusive, shared and invalid) which allow to determine whether two transactions are accessing memory locations in a conflicting manner. As soon as a conflict is detected, the usual strategy adopted by HTMs consists in aborting the transaction and passing the control to a software handle to either use a fallback path or re-execute the transaction.

The hardware support for transactional memories is now a mature feature of processors: the next two sections provide a description of two commercial examples of HTMs that were used for this thesis.

#### 2.1.5 POWER8

The *POWER8* processor, by IBM, features twelve cores, each having at disposal its own Level2(L2) cache, with a capacity of 512KB, and and Level3(L3) cache, capable of storing information up to 8MB. There are also two memory controllers (both third generation PCI Express) and a bus providing connection among all the components. Each core (64 bit) supports multithreading, being able to simultaneously run up to 8 threads, and is provided with a 32KB eight-way associative Level1(L1) cache for instructions and a 32KB eight-way associative Level1(L1) cache for data [12].

#### **Transactional Memory Implementation**

POWER8 is the first processor, based on POWER ISA, that supports transactional memory: the instruction set is extended with a set of machine instructions to implement and control the execution of transactions. The implementation is *best-effort*, namely there is no guarantee that a transaction will eventually commit. In case of failure, a dedicated register, the Transaction Exception and Status Register (TEXASR), is initialized to a code (eight different values are possible on POWER8) that gives an indication of what prevented the transaction from committing; another register, the Transaction Failure Instruction Address Register (TFIAR) is instead set to the address of the instruction responsible for the failure. More importantly,

9

behaviour of the handler consists in reading the value of the two registers and deciding, depending on the cause of the failure, whether it is worthy to try reexecuting the transaction or if it is better to abort it. Transactions can be nested (up to 62 levels), but the results of the commit of a inner transactions are not made available until the outer transaction correctly finishes too; if a transaction, at any level of nesting, aborts, the whole stack of transactions aborts too. The programmer requests for the beginning of a transaction in a thread issuing the **tbegin** instruction. The Machine Status Register (MSR) is used to determine whether an execution path is running inside a transaction or not. These two conditions correspond to the Transactional and Non-Transactional state respectively; the third possible state is Suspended (see later). The begin instruction causes the underlying implementation to first make a checkpoint of the current state of the hardware registers; then it checks whether other threads are concurrently executing the operations on the same shared data outside the scope of a transaction. If that's so, the transaction can not proceed and it is aborted by the tabort instruction, which gives control to the software handler. Otherwise, the transaction can continue till the end. During the execution, write operations to memory are performed *speculatively*, namely their effect are made visible only after the transaction eventually commits, otherwise they are cancelled. If two different threads access the same cache line and either one or both are currently running a transaction, a conflict arises, causing either of the transactions to fail. The size of a cache line determines the capability of the implementation of detecting false conflicts (those situations where two threads are actually accessing different memory locations but these operations are still recognized as conflicting because the two addresses are stored in the same cache line). In case of POWER8, the cache line has a size of 128 bytes [24]. The programmer can also temporarily suspend a transaction with the **tsuspend** instruction: from that point on, the instructions will not be included in the transaction, so their effects will not be undone should the transaction later fail; indeed, the cache lines used by the transactions before it was suspended keep being monitored, so if a conflict takes place the transaction will fail as soon as it is resumed with the tresume instruction. The possibility of suspending transactions serves for debugging purposes and for the transaction itself to continue after an interrupt has occurred. The end of a transaction is marked by the programmer with the instruction tend: if the transaction can successfully commit, its associated write operations are atomically committed for all the other threads to see them; the effects of multiple transactions are applied following a serial order. Otherwise, if the transaction can't commit, the software handler usually tries to re-run it for a limited number of times; if it never succeeds, the code of the transaction is executed acquiring the lock that protects the critical section [19].

#### **Transactional Memory Architecture**

Fig. 2.1 (the image taken from [19]) provides a clear illustration of the internal hardware architecture of POWER8: what follows gives a brief explanation of its most important elements. The Instruction Sequencing Unit (ISU) stores in the core the checkpoint of the registers created every time a new transaction begins. The Load Store Unit (LSU) of each core contains a Level1 private cache where are

Figure 2.1. The HTM architecture on POWER8

stored the addresses written by the transaction. In particular, for each cache line the L1 Directory (L1Dir) includes two extra bits that are set to respectively indicate whether the cache line has been accessed inside a transaction and the ID of the thread executing it. Cache lines involved in a transaction are not available to other threads until the commit or the abort of the transaction itself: any attempt of access is translated to a cache miss and handled by L2 cache. The TM Load Directory (TM LD DIR) keeps a reference to the addresses read by transaction, which are maintained in the L2 cache, and serves to reduce transfers to the L1 cache. In the L2 cache, the TMCAM is a directory with 64 entries, each containing a cache line address and several bits that indicate its state for each single thread. Conflicts are detected by the TMCTL unit of the L2 cache, which keeps an eye on the memory locations accessed by not only the local core, but also by the other cores. When a conflict actually occurs, the core running the aborted transaction gets informed by the TMCTL unit and the software handler is activated. Finally, the TMCAM in the L3 cache keeps track of dirty cache lines accessed by a transaction during its execution, until it eventually fails or commits.

The size of the described hardware resources, necessary for the hardware implemen-

tation of the transactional memory, puts a limit on the total number of memory addresses that can be accessed inside a transaction. When a transaction tries to overcome this limit, the transaction is aborted: such a kind of abort is referred to as *capacity-overflow abort* [24].

#### 2.1.6 Intel Haswell

Haswell [13] is the fourth-generation family of Intel Core processors, by Intel. According to jargon used by Intel to classify the advancements in the architectures of CPUs, it is a "tock", meaning that it represents a big step with respect to the microarchitecture of its predecessor, Ivy Bridge. Despite the main improvements affect the area of power management and efficiency, Haswell features, for the first time in the history of Intel architectures, a new set of instructions taht provide support for transactional memories: this extension of the ISA is called *Transactional Synchronization Extensions (TSX)* (see Section 2.2.1).

Whereas plenty of information is available regarding the interface exposed to programmer for them to take advantage of the transactional memory support, it is way more difficult to find details about its underlying implementation, since they were not disclosed. It is sure [13] that the Level1 cache, whose capacity is 32KB, serves to maintain the memory addresses accessed by the transaction during its execution, for both load and store instructions. Moreover, conflict detection relies on cache coherency protocols. Some <sup>2</sup> speculated about the rest of the implementation, formulating the hypothesis that write operations are first executed on cache lines, saving the original data present in memory in a shared L3 cache.

#### 2.2 Transactional Lock Elision

Transactional lock elision (TLE) is a technique that exploits hardware transactional memories to execute simultaneously on multiple threads critical sections that otherwise would be serialized by a synchronization primitive, running sequentially. The programmer is required to define the boundaries of the critical section to be run in parallel and the processor, at runtime, avoids taking the lock which protects the critical section and executes it in parallel on multiple threads in a "transactional way". This means that the processor does not actually execute the write operation directly to memory, but buffers them waiting for the outcome of the transaction; analogously, it tracks all the memory addresses read. At the end of the transaction, if there was no conflict in the access of shared data by concurrent threads, the processor atomically applies the buffered store operations to memory. If that is so, the lock has been "elided", since the critical sections have been executed in parallel without synchronizing the access to shared data and still ensuring isolation, consistency, durability and atomicity (the properties inherited from the transactional semantics). Otherwise, if the transaction fails, the state of the system is restored to the moment antecedent to its start. The next two sections contain a description of the interface offered to the programmer for the definition of transactions by the two architectures described before.

$<sup>^{2}</sup>$ realworldtech.com/haswell-tm

#### 2.2.1 Intel Transactional Synchronization Extensions

Starting from the family of processors Haswell (see Section 2.1.6), Intel adopted a new instruction set, Intel TSX, that comprises two software interfaces for programmers to request transactional lock elision:

- 1. Hardware Lock Elision (HLE)

- 2. Restricted Restricted Transactional Memory (RTM)

The underlying implementation is best-effort, meaning that transactions are not guaranteed to always commit, even in absence of concurrency, because of conflicts or capacity aborts. Another reason for failures is the execution of machine level instructions that are guaranteed to cause transactions to abort, like CPUID or PAUSE <sup>3</sup>. It is up to the programmer to ensure that these kind of instructions are not included in a transaction, as well as to try avoiding the following (partial) list of instructions, which might may cause an abort too:

- system calls (SYSENTER, SYSCALL, SYSEXIT, SYSRET)

- interrupts (INTn, INTO.)

- I/O instructions

- updates to some portions of the EFLAGS register

- saving the state of the processor (XSAVE)

HLE is an extension of the machine instructions set that introduces two new instruction prefixes, XACQUIRE and XRELEASE, to mark respectively the beginning and the end of a transaction. The two prefixes are ignored on legacy architectures that do not have the transactional support, hence HLE is the recommended choice for programmers that intend to run their code on the broadest set of architecture as possible. The mechanism associated with HLE tries to run the code comprised between the two prefixed instructions as a transaction: in case of abort, there is no further attempt to make the transaction commit.

RTM, on the contrary, although relies on the same hardware resources, is capable of offering the developers more flexibility in the management of the transactions. It is a new set of instructions that a programmer has to use in his code to handle transactions:

- XBEGIN serves to define the beginning of a transaction and takes in input the address of a *fallback function*, which is passed the control of the execution if the transaction does not successfully commit. One common behaviour for this software handler is to try re-executing the transaction a number of times: in case all the attempts are not successful, the critical section is executed in a non-transactional way grabbing the associated lock

- XEND marks the end of the transaction

<sup>&</sup>lt;sup>3</sup>software.intel.com/en-us/node/524022

• XABORT allows to explicitly abort an ongoing transaction, also specifying the motivation of this action through an 8-bit value

```

retries = N RETRIES

1

\mathbf{2}

status = XBEGIN()

3

lock = init_lock()

if status != ok:

4

\mathbf{5}

if retries == 0:

6

lock.acquire()

7

else:

8

retries ---

9

goto 2

10

if islocked(lock) == true:

11

XABORT

12

CRITICAL SECTION

13

14

15

if attempts = 0:

16

lock.release()

17

else

18

XEND

```

Listing 2.2. Transactional Lock Elision with TSX

In case of abort of a transaction, even due to a call to XABORT, the implementation sets the bits of the EAX register in order to indicate the reason of the failure. The following is an explanation of the meaning associated with each bit of the register in case of abort:

- bit 0: set if XABORT was called

- bit 1: set if a re-execution of the transaction might commit successfully; cleared if bit 0 is set

- bit 2: set in case of conflicting access to shared data

- bit 3: set in case of buffer overflow

- bit 4: set in case of debugging point being hit

- bit 5: set in case of abort of a nested transaction

- bits 24 to 31: contain the 8-bit value passed by XABORT

#### 2.2.2 POWER ISA Transactional Memory Support

As already anticipated in 2.1.5, POWER 8 is the first family of microarchectures manufactured by IBM to have the transactional memory support. The new instruction set has an extension that, similarly to Intel, allows programmers to run a critical section speculatively, without first acquiring the lock and possibly bypassing (or

"eliding") it. The boundaries of the code to be executed speculatively are defined by the programmer with the machine level instruction tbegin and tend; a running transaction can be momentarily suspended with the tsuspend instruction and later restored with the tresume instruction. Like Intel TSX, also the POWER ISA implementation is best-effort, so when a transaction starts, a checkpoint of the actual state of the registers (so called *pre-transactional state*) is automatically created: in case of a premature interruption of the transaction, the condition of the system is rolled-back to this initial state. Privileged users can access the values of the checkpointed registers by mean of the treclaim instruction; conversely, the trechkpt instruction places the checkpoint back to the dedicated registers. If a transaction fails (either because of external factors or because of an explicit termination requested by the programmer through tabort), the control has to be redirected to a software handler. In particular, the CRO register is initialized to the value 0b1010 in case the transaction cannot be successfully start, to the value 0b0100 otherwise. As a consequence, the instruction following tbegin has to be a branching instruction, for example beq (branch on equal), that checks the value of the CR0 register and gives control to a software handler in case of failure.

```

start_transaction:

1

\mathbf{2}

tbegin

# Start transaction

3

software handler

# Branch on value of CR0

beq

CRITICAL SECTION

# Critical section

4

# End transaction

5

tend.

b

6

transaction_exit

# Continue execution after

7

\# a transaction has terminated

software handler:

8

9

r4, TEXASRU

\# Read the value of

mfspr

10

# the TEXASR register

andis. r5, r4, 0x0100

# Check if the failure

11

12

# is persistent

13

bne

acquire_lock

# If it is persistent,

14

\# acquire the lock

\# to run the critical section

15

16

b

start transaction

# If not persistent, try again

17

18

acquire_lock:

19

20

transaction exit:

```

Listing 2.3. Transactional Lock Elision with POWER ISA

A failure is either *transient* or *persistent*: in the former case, the abort of the transaction was caused by a temporary condition of the system, so there are chances that the transaction commits on a new attempt; in the latter case, instead, there are no possibilities for a successful completion of the transaction, so the strategy adopted in this case consists in acquire the lock and run the critical section in non-transactional way. The software handler leverages the content of the **TEXASR** (see Section 2.1.5) register to determine the cause of the failure. More precisely, the

first 6 bits of this 32 bit register contain the transaction failure code; the seventh bit is set in case of persistent failure [12].

#### 2.2.3 GCC Transactional Memory Interface

On machines based on POWER ISA, like POWER 8, developers can take advantage of the transactional memory facility through *GCC (GNU Compiler Collection)*. There are three possible choices [12]:

- 1. using the HTM low-level built-in functions

- 2. using the HTM high-level built-in functions

- 3. using the *libitm* library

The first set of functions is enabled compiling the source code with the -mcpu=power8 or -mthm options. All these functions return the 4-bit value written by the corresponding machine level instructions in the TEXASR register; the header file htmintrin.h includes some helper functions to parse and return this value. The macro that starts a new transaction, \_\_builtin\_tbegin does not adhere to this procedure and returns instead a boolean value indicating whether a transaction has been successfully started. The listing below shows a pattern of usage of the functions.

```

#include <htmintrin.h>

1

\mathbf{2}

3

int num_retries = 10;

4

\mathbf{5}

while (1)

6

{

if(\__builtin\_tbegin(0))

7

8

9

/* Transaction State Initiated.

*/

if (is_locked (lock))

10

___builtin_tabort (0);

11

12

... transaction code ...

\__builtin_tend (0);

13

14

break;

15

}

else

16

17

{

Transaction State Failed. Use locks if the

18

transaction

failure is "persistent" or we've tried too many

19

times. */

if (num retries - < = 0

20

|| TEXASRU FAILURE PERSISTENT (

21

__builtin_get_texasru ()))

22

{

acquire_lock (lock);

23

```

```

24 ... non transactional fallback path...

25 release_lock (lock);

26 break;

27 }

28 }

29 }

```

Listing 2.4. Low-level HTM GCC built-in functions on POWER ISA

The code above <sup>4</sup> tries to execute speculatively the code corresponding to a critical section (transaction code) until either the associated transaction (identified by the integer passed to \_\_builtin\_tbegin) commits or a limit for the number of attempts (num\_retries) is reached. As soon as the transaction starts, the code checks whether other threads are concurrently executing the same critical section acquiring the lock that protects it (see Section 2.1.5). If that is so, the transaction is explicitly aborted by \_\_builtin\_tabort; otherwise it proceeds until the end of the critical section, which is marked by \_\_builtin\_tend. In case of failure of the transaction, the software handler (corresponding to the else branch) reads the value of the TEXASR register with \_\_builtin\_get\_texasru and thanks to the utility function \_TEXASRU\_FAILURE\_PERSISTENT determines if it is worthy to try re-executing the transaction. If this is not so, the fallback path, namely the lock-protected execution of the critical section, is taken.

The second group of functions is intended to make the code more portable, since it can be compiled not only by GCC, but also by IBM XL; programmers have to include the header htmxlintrin.h to use this interface.

Finally, the highest level interface available is represented by *libitm*, the GNU*Transactional Memory Library*<sup>5</sup>. At runtime, it transparently verifies whether the underlying hardware supports transactional memory and, if so, wraps a transaction around the critical section specified by the programmer as in the listing below. The integration of this

```

_____transaction__atomic {

```

2 CRITICAL\_SECTION;

3

}

1

16

Listing 2.5. Transactional code using libitm

GCC also offers support for programmers to use hardware transactional memories on machines based on Intel TSX. The RTM interface (see Section 2.2.1) can be accessed adding -mrtm to the flags passed to the compiler and comprises four functions (see the code <sup>6</sup> below:

• xbegin starts a transaction. If this operation is successful, \_XBEGIN\_STARTED is returned; if the transaction is aborted, besides undoing its effects, this function stores in the EAX register a code indicating the reason for the abort and

$<sup>^4 \</sup>rm gcc.gnu.org/onlinedocs/gcc/PowerPC-Hardware-Transactional-Memory-Built-in-Functions.html$

<sup>&</sup>lt;sup>5</sup>gcc.gnu.org/wiki/TransactionalMemory

<sup>&</sup>lt;sup>6</sup>gcc.gnu.org/onlinedocs/gcc-4.8.1/gcc/X86-transactional-memory-intrinsics.html

returns it. This provides the software handler with the information necessary to decide to either retry the transaction or not

- xend commits a transaction. If this operation is successful, the effects of the operations inside the transaction are applied atomically, otherwise the state of the registers is restored to the state antecedent to the transaction

- xabort explicitly aborts a transaction (including nested transactions); the constant to be passed as parameter is written into the upper eight bits of the EAX register

- **xtest** serves to check if a transaction is currently active: 0 is returned if that's not the case

```

#include <immintrin.h>

1

2

3

int n_tries , max_tries;

unsigned status = _XABORT_EXPLICIT;

4

5

. . .

6

7

for (n_tries = 0; n_tries < max_tries; n_tries++)

8

{

9

status = xbegin();

if (status = _XBEGIN_STARTED || !(status &

10

_XABORT_RETRY))

11

break;

12

}

13

i f

(status == XBEGIN STARTED)

14

{

... transaction code...

15

16

xend();

}

17

18

else

19

ł

20

... non-transactional fallback path...

21

ł

```

Listing 2.6. Transactional code using the GCC RTM interface

The HLE interface (see Section 2.2.1) is accessible through the atomic built-in functions, which allow to synchronize the access to memory locations by multiple threads in such a way that read and write are made visible atomically. A transaction is started by the following snippet of code  $^7$

```

1 /* Acquire lock with lock elision */

2 while (___atomic_exchange_n(&lockvar, 1, __ATOMIC_ACQUIRE)

___ATOMIC_HLE_ACQUIRE))

```

$<sup>^7{\</sup>rm gcc.gnu.org/onlinedocs/gcc/x86-specific-memory-model-extensions-for-transactional-memory.html}$

\_mm\_pause(); /\* Abort failed transaction \*/

Listing 2.7. Start transaction with HLE

and finished by this piece of code  $^7$

1

/\* Free lock with lock elision \*/

2

\_\_atomic\_store\_n(&lockvar, 0, \_\_ATOMIC\_RELEASE)

ATOMIC HLE RELEASE);

Listing 2.8. End transaction with HLE

#### 2.3 TensorFlow

#### 2.3.1 Introduction

Ever since it was released by Google in 2015, TensorFlow (TF) has become one of the most successful open-source software library for building and training machine learning models, especially deep-neural networks [11]. TF is the successor of DistBelief [2], a system for large-scale deep learning developed within the Google Brain project for internal usage: in particular it was meant to support research and to implement some of the functions of Google products like Google Maps or YouTube. Besides the fact that DistBelief is not open-source, TF was introduced to overcome the limits of its predecessor[1]. In particular, TF is intended to ease the definition of new architectures for the layers of the neural networks, as well as the experimentation of various optimizations for the training algorithms. Furthermore it allows to model further kinds of neural networks, like recurrent neural networks. More importantly, TF is not only capable of scaling-up to train on big amount of data, like DistBelief, but it can also scale-down to allow training networks even with limited hardware resources at disposal. As a result, TF can be run on a plethora of heterogeneous platforms, ranging from mobile devices to large-scale training systems featuring many GPUs.

The core of the library is implemented in C++ and exposes an API for the following programming languages: Python, C++, Java and Go; actually the first one is the recommended and most complete API. The logical organization of a client program that makes use of TF comprises two sections <sup>8</sup>:

- 1. a dataflow graph is built in order to represent the computation and the state associated with the desired machine learning algorithm

- 2. an optimized version of the dataflow graph is executed on the devices specified in the code

Postponing the execution, this can be optimized exploiting the information provided by the representation of the computation [1].

$\mathbf{18}$

3

<sup>&</sup>lt;sup>8</sup>tensorflow.org/get\_started/

#### 2.3.2 Building the Dataflow Graph

Following the dataflow programming model [29], a TF program is internally modelled as a directed acyclic graph where the nodes correspond to the computation to be performed; the edges carry the input data to the nodes and gather the resulting output data. The choice of such paradigm is motivated by the following advantages 9:

- 1. the explicit connections between the nodes enable to rapidly determine the operations that can be executed in parallel

- 2. the computation can be distributed across multiple devices

- 3. it is possible to apply some linear algebra optimizations during the compilation and produce a faster code

- 4. the dataflow can be expressed in various programming languages, so it is portable

In TF each node of the graph is referred to as *operation* and represents the fundamental unit of computation: it is assigned a unique name and has a non-negative number of input and output data [1]. Each operation is executed on a *device*([[2]), like a CPU or a GPU, characterized by a type and a name. A *kernel* is the implementation of an operation optimized for a certain device, so for a single operation there are as many as kernels as the number of devices where the operation can be performed. Most of readily available kernels of TF rely on the *Eigen library*, which exploits C++ template to parallelize the execution of the code. Developers can add their own operations and related kernels into the library via a simple registration mechanism [1].

As the name suggests, in TF data flow along the edges under the form of *tensors*, namely *n*-dimensional arrays characterized by a primitive data type (integer, float, string) and a shape (the number of elements in each dimension) <sup>10</sup>. Training models usually implies multiple executions of the same dataflow graph: the lifetime of a tensor coincides with the duration of a single iteration and it maintains the same value throughout it. An exception to this rule regards the tensors returned by *variables* <sup>11</sup>. A variable is a special kind of operation, with no input, holding an internal buffer where values can be stored, modified and retrieved. Since variables survive a single execution of the graph, they are used to maintain the parameters of the models learned iteration after iteration. Another special kind of operation is the *queues*: like variables, queues persist values across successive executions using an internal mutable buffer, but unlike the former they implement the logic of a queue data structure.

#### 2.3.3 Executing the Dataflow Graph

After having constructed the dataflow graph, it has no utility if it is not executed, because it is during the execution that the nodes are processed and produce a

$<sup>^{9}</sup> tensorflow.org/programmers\_guide/graphs$

$<sup>^{10}</sup> tensorflow.org/programmers\_guide/tensors$

$<sup>^{11}</sup> tensorflow.org/programmers\_guide/variables$

result. A Session object is the interface provided by the API for a client program to request the execution of the graph to the TF runtime, in particular invoking its Run method [1, 2]. This method has to be given a list with one or more *fetches*, namely the operations that have to be executed or the tensors that have to be evaluated. The C++ back-end automatically determines the subset of the nodes of the dataflow graph that have to be considered in order to satisfy the request and also the order in which they have to evaluated. This subgraph comprises the operation nodes in the provided list and all the other nodes whose outputs determine the inputs to the fetches. The user can control the execution providing input data under the form of *feeds*, i.e. a mapping between tensors present in the graph and the values to be assigned to them; typically these tensors are the *placeholders*, nodes through which a client program can feed data into the graph. Every execution of the Session through its Run method represents a *step* of the computation and TF allows concurrent executions of the same graph. By default there is no coordination between concurrent executions, which makes it possible to implement training algorithms where consistency is not required, but synchronization primitives are also provided when more guarantees are needed.

#### 2.3.4 Visualizing the Dataflow Graph

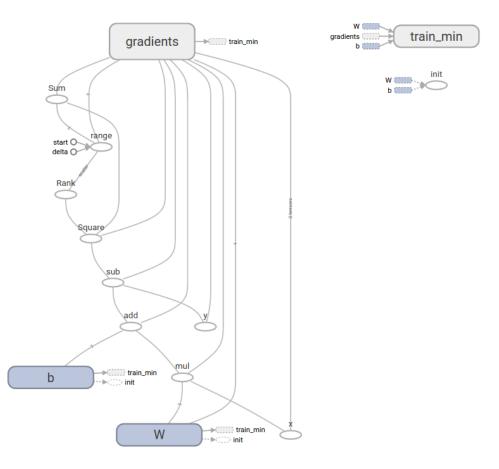

The number of nodes of the dataflow graphs associated to some complex machine learning models can be over a few thousands, so it might be tricky trying to check how the computation is performed. In TF this problem is solved by *TensorBoard*, a tool that manages to provide a simplified yet complete and interactive visualization the dataflow graph created by a client program [2]. TensorBoard also allows to monitor many other metrics regarding the training of the model, like the value of the loss function or the values of the weights. To realize all this, the tool extracts all the information from special events files produced during the execution of the dataflow graph thanks to some *summary operations*. These special nodes have to be added to the graph by the developer and connected to those other nodes from which he/she wants to collect the information to be later visualized. When the dataflow graph is run, the summary operations generate the events file needed by TensorBoard and the graphical representation of the computation gets accessible at port 6006 of the local host. Below are a piece of code that computes the sum between the matrices in TF and the visualization of the corresponding dataflow graph in TensorBoard.

```

import tensorflow as tf

1

\mathbf{2}

3

\# the placeholder for the input matrices

A = tf.placeholder(tf.int32, [2, 2], "A")

4

B = tf.placeholder(tf.int32, [2, 2], "B")

5

6

7

\# the Operation node that computes the sum of the two

matrices and

8

\# returns the resulting matrix

9

C = tf.add(A, B)

10

\# the Summary operation to visualize the graph

11

```

```

summary = tf.summary.tensor summary("Sum", C)

12

13

14

\# create a Session using the context manager

15

with tf.Session() as sess:

16

17

\# run the graph: provide a dictionary of values to

initialize the input

\# matrices and compute the sum of the matrices.

18

Serialize the summary data

# into the "summary" protobul object

19

20

summary, \_ = sess.run([summary, C], {A: [[0, 1], [1,

0]], B: [[1, 1], [0, 1]])

21

22

# instantiate a FileWriter to write the serialized

object to the disk

23

writer = tf.summary.FileWriter('.', sess.graph)

24

25

\# write the serialized object to the disk

26

writer.add_summary(summary)

```

Listing 2.9. Add matrices in TensorFlow

#### 2.3.5 Architecture

As soon as it has created the dataflow graph, the client program instantiates a Session, which serializes the graph and passes it to the core runtime of TF through an intermediate layer represented by a C API. The runtime of TF is composed of two main components:

- distributed master

- worker service(s)

The distributed master extracts from the entire dataflow graph the subset of nodes whose execution is necessary to evaluate the nodes indicated in the Session. The resulting portion of the dataflow graph is partitioned into one or more subgraphs, which are optimized and cached to make successive training steps quicker [1, 2]. The distributed master then schedules the execution of the subgraphs through a set of *tasks*, each running as a single operating system process. A task is responsible for the access to one or more devices and is associated with a *worker service* (a.k.a. *dataflow executor*). This receives the subgraphs from the master and decides the execution of the kernels corresponding to the operations across the set of available devices; when possible, kernels are executed in parallel (for instance using multiple CPU cores).

Two implementations of the above described architecture are available [2] (image was taken from  $^{12}$ ):

$<sup>^{12}</sup>$ tensorflow.org/extend/architecture

Figure 2.2. Dataflow graph relative to Listing 2.9

- *local*: the client, the master and one worker service all reside in the same process on a single machine

- *distributed*: the client, the master and multiple workers belong to the different processes on different machines connected over the network

In both cases, there are two possible scenarios:

- single-device execution

- multiple-devices execution

When only one device is available, a single worker service schedules the execution, for each operation node, of the kernel corresponding to the present device. If more the one device is eligible for running the nodes of the computation graph, the runtime of TF has to decide where to place the nodes and also hat to handle the communication between the devices in order to coordinate the execution. The algorithm adopted to determine the placement of the nodes takes into account parameters like the size of input and output tensors of a node and an estimation of the computation time required. After a simulation of the execution of the graph, the algorithm assigns each node to a device. This causes a partitioning of the original graph into as many

Figure 2.3. Architecture of TensorFlow

subgraphs as the number of devices. The starting and ending vertices of each edge of the original graph connecting two nodes assigned to different devices are respectively replaced by two new nodes *Send* and *Receive*. In this way, after the partitioning, those tensors that flowed along the replaced edge are transferred from one device to another. The actual realization of the two communication operations depends on the involved devices [1]:

- local transfers between a CPU and a GPU use the cudaMemcpyAsync() API

- local transfers between GPUs rely on Direct Memory Access

- transfers over the network between worker services adopt various protocols, mostly gRemoteProcedureCall(gRPC) and RDMA over Converged Ethernet

#### 2.4 Statistical Learning

#### 2.4.1 Overview

This area [16] deals with the solution of problems where, given a set of *input variables*  $X_1, X_2...X_n$  and an *output variable* (or *dependent variable*) Y, it has to be found an estimation of the function f such that  $Y = f(X) + \epsilon$ , being  $\epsilon$  an error term. The estimated function serves to predict the output corresponding to a certain input(s) or to understand the relation between input and output variables. Statistical learning requires the *training data*, namely a set of pairs  $(x_i, y_i), i = 1...m$  where  $x_i$  and  $y_i$  are respectively the value(s) of the *i*-th observation for the input variable(s) and the corresponding value of the output variable. The estimation of the function f is

obtained through the application of a *learning method* to the these data. There are two main kinds of learning methods:

- parametric methods: they assume that the function f is approximated by a parametric model so the estimation of f is made finding the parameters of the models that minimize the distance between the function and the model themselves

- non-parametric methods: no assumption is made about the shape of f, so these methods usually achieve a better accuracy in the estimation at the cost of a higher number of observations.

So far we considered training data where for each value of the input variables observed the corresponding value of the output variable is known: in this scenario the training of the model is said to be *supervised*. Unfortunately it is sometimes the case that the values of the output variable are not known, which makes the training more difficult. The methods applied in this setting perform an *unsupervised learning*. Examples of the supervised learning are *liner and logistic regression*, while examples of unsupervised learning are *clustering methods*. A further classification of the problems tackled by statistical learning regards the kind of the variables involved: the domain of *quantitative variables* is numerical, while the domain of *qualitative variables* is a set of *classes*. Problems dealing with quantitative variables are referred to as *regression problems*, while those related to qualitative variables are known as *classification problems*. Given the variety of the learning methods available, a metric to evaluate their performances is needed in order to decide which of them achieve the best results for a certain dataset.

In case of regression problems, the chosen metric is usually the mean squared error (MSE) and it is calculated over the test data. This is a set of pairs  $(x_i, y_i)$ , where  $x_i$  is the observed value(s) of the input variable(s) and  $y_i$  is the related value of the output variable, that is disjoint from the training set. Indeed it is not important that model performs well on the instances of the input values used for the training, but rather on unseen instances, because this ensures that it can predict the output with good accuracy for a future usage. Being m the number of test data pairs available and  $\hat{f}$  the trained model, i.e. the estimation of the function f, the test MSE is defined as follows:

$$MSE_{test} = \frac{1}{m} \sum_{i=1}^{m} (y_i - \hat{f}(x_i))^2$$

Obviously, the smaller the test MSE, the better is the performance of the learning method. A risk associated with learning methods is *overfitting the data*, namely training the model in such a way that it is tightly connected to the training set. The negative consequence is that even though the model is accurate on training data, it does not perform well on test data.

As regards with classification problems, where the estimated function f determines the class which the input value belongs to, the measurement of the performances of the learning methods is based on the number of wrong classifications. Given  $\hat{y}_0$  and  $y_0$  respectively the estimated class and the actual class (or *label*) of the input value  $x_0$ , the *indicator variable I* returns 1 if  $\hat{y_0} \neq y_0$  and 0 otherwise. In other words, *I* returns 1 when a value is misclassified. Using the indication variable, it is possible to evaluate a classification algorithm through the *test error*, which is defined as the average value of the indicator variable over the test data. To put it simply, it coincides with the number of misclassifications over the number of test data, so the smaller is this value, the better is the classifier.

#### 2.4.2 Linear Regression

Linear regression is a supervised learning method to predict the quantitative output variable Y given an input variable X, assuming the existence of a linear relation between them. In simple linear regression Y is approximated by the model  $\beta_0 + \beta_1 X$ : the training phase returns the estimation of its parameters, respectively  $\hat{\beta}_0$  and  $\hat{\beta}_1$ . The most common approach for the estimation of the parameters is by far the minimization of the least squares. For each value  $\hat{y}_i$  of the output variable predicted by the model as function of the input value  $x_i$ , a residual  $e_i$  is defined as the difference between the actual value  $y_i$  corresponding to  $x_i$  and the predicted value. The residual sum squares (RSS) is the sum of the squares of the residuals of all the values of the input variable. Applying some calculations it is easy to show that the values of the parameters of the model that minimize the RSS are the following (considering m possible values for the input variable):

$$\hat{\beta}_{1} = \frac{\sum_{i=1}^{m} (x_{i} - \bar{x})(y_{i} - \bar{y})}{\sum_{i=1}^{m} (x_{i} - \bar{x})^{2}}$$

$$\hat{\beta}_{0} = \bar{y} - \beta_{1}\bar{x}$$

with  $\bar{y}$  and  $\bar{x}$  the average value of the output and input variable respectively. When there are more than one input variables, simple linear regression is extended to *multiple linear regression*. Here the relation between the output variable and the *n* input variables is modelled by the equation  $y = \beta_0 + \beta_1 X_1 + ... \beta_n X_n + \epsilon$ . Also in this case, an estimation of the parameters  $\hat{\beta}_0, \hat{\beta}_1...\hat{\beta}_n$  is obtained minimizing the RSS.

#### 2.4.3 Logistic Regression

In a classification scenario, where the output response is qualitative (a class or a category), linear regression is to be replaced by *logistic regression*, which takes into account the probability that the output corresponding to a set of input values falls into a certain class. On the basis of such probability, it is possible to estimate the category which the input data belong to. For example, in case of binary class, given  $p_1(X) = Pr(Y = 1|X)$ , the estimated class of X is 1 if  $p_1(X) > 0.5$ , 0 otherwise. The linear model is no longer suitable to express the relation between input and output variables: indeed, because of the introduction of probability, there is the need of a function resembling a density function, whose response is comprised in the interval [0, 1]. The approach of logistic regression consists in modelling the likelihood of a certain class k conditioned to the input values using a *logistic function* (or *logistic sigmoid*)  $p_k(X)$  ([[3, 16]), with  $p_k(X)$  defined as follows:

$$p_k(X) = Pr(Y = k|X) = \frac{e^{\beta_0 + \beta_1 X}}{1 + e^{\beta_0 + \beta_1 X}} = \frac{1}{1 + e^{-\beta_0 - \beta_1 X}}$$

Given the assumption of a binary class, the input corresponds to either of the two possible values of the class, so it holds  $p_0(X) = Pr(Y = 0|X) = 1 - Pr(Y = 1|X) = 1 - p_1(X)$ . This can be expressed more concisely as

$$p(y|X) = p(X)^y + (1 - p(X))^{1-y}, y \in \{0, 1\}$$

which corresponds to the density function of a Bernoulli distribution. In this case, fitting the model means finding those values  $\hat{\beta}_0$  and  $\hat{\beta}_1$  such that, for each input  $x_i$  of the training data,  $\hat{p}(x_i)$  it holds:

$$\hat{p}(y|x_i) = \left(\frac{1}{1 + e^{-\hat{\beta}_0 - \hat{\beta}_1 x_i}}\right)^y + \left(1 - \frac{1}{1 + e^{-\hat{\beta}_0 - \hat{\beta}_1 x_i}}\right)^{1-y}$$