## Speculative Read-Write Locks

Tiago João dos Santos Lopes

Mestrado em Engenharia Informática e Computadores Information Systems and Computer Engineering

Supervisor: Dr. Paolo Romano

Draft

May, 2018

## Resumo

Memória Transacional (TM) é uma abstração para programação paralela promissora, que tem sido recentemente implementada em hardware por produtores principais como a Intel e IBM. Hardware Transactional Memory (HTM) expõe aos programadores, através de uma extensão dedicada das suas instruções de processador, uma implementação assistida por hardware, e altamente eficiente, da abstração de transações atómicas.

Vários trabalhos recentes têm mostrado que HTM consegue reduzir significativamente o custo de sincronização sofrido por aplicações paralelas em várias áreas. Infelizmente, também já foi identificado por vários estudos que implementações HTM atuais sofre de graves limitações, em grande parte devido á natureza restrita de mecanismo *best-effort* que o hardware utiliza.

Estas restrições do design limitam a aplicabilidade de HTM de várias formas: não só restringe o número de posições de memória acessíveis pela transação, também faz com que as transações de hardware incapazes de de suportar eventos tais como chamadas de sistema, perdas de processador *context switching* e pedidos de interrupção. Desta forma as restrições mencionadas tornam os sistemas HTM atuais incapazes de servir como mecanismos de sincronização polivalentes, o que limita a sua utilização.

Este trabalho tenta combater exatamente este problema apresentando Speculative Read Write Lock (SpRWLock), um novo mecanismo de sincronização baseado em HTM com um ponto-chave: permite blocos atómicos de leitura executa fora do sistema de transações em hardware, effectivamente poupando-as das limitações existentes nas atuais implementações HTM.

Speculative Read Write Lock (SpRWLock) combina duas técnicas novas com o objetivo de asseguras a safety e maximizar eficiência.

SpRWLock preserva a *safety* de blocos atómicos de leitura, correndo fora do alcance de transações de hardware, através de uma simples, mas supreendentemente eficiente, técnica: obrigas as transações de escrita, que executam em HTM, que verifiquem, no momento de submissão, verificar se existem blocos atómicos de leitura ativos, e permitindo a submissão dos escritores apenas se nenhum for encontrado; caso contrário abortam a transação HTM.

Esta técnica consegue obter impressionantes (até  $6 \times$ ) ganhos de processamento comparado ao sistema base HTM em cargas de trabalho (*workload*) que contenham grandes blocos atómicos de leitores. No entanto esses ganhos de processamento são obtido á custa de um aumento no periodo de latência de blocos de escritura atómicos, que chegam a abortar diversas ver (e teóricamente ser privados de executar) em *workloads* onde leitores grandes são predominantes.

SpRWLock foca neste problemas complementando o algoritmo base acima descrito com dois esquemas ad-hod de calendarização, as quais referimos de sincronização de leitores e sincronização de escritores.

Avaliamos SpRWLock através de um estudo experimental extensivo utilizando as implementações HTM disponíveis nos CPUs *Broadwell* da Intel e *Power8* da IBM e abrangendo micro-benchmarks destinadas a avaliar a sensibilidade da solução proposta a um spectro de *workloads*, bem como benchmarks padrão (TPC-C, STM-Bench7) e aplicações reais (KyotoDB). Os resultados do nosso estudo mostram que SpRWLock consegue ganhos de desempenho até  $15 \times$  em relação tanto a soluções HTM base, como também ao estado de arte atual, Implementações de trincos em leitores-escritores de forma não especulativa *non-speculative read-write lock implementations*.

iv

# Palavras-Chave

memória transacional, sincronização, leitores-escritores, elisão de trincos, hardware

# Abstract

Transactional Memory (TM) is a promising abstraction for parallel programming, which has recently been implemented in hardware by mainstream like Intel and IBM. Hardware Transactional Memory (HTM) provides a highly-efficient, hardwareassisted implementation of the abstraction of atomic transaction, long used in the context of database systems, and now exposed to programmers/compilers via a dedicated extension of the processor instruction set.

A number of recent works have shown that HTM can reduce significantly the synchronization overheads incurred by parallel applications in various application domains. Unfortunately, though, several studies have also highlighted that existing HTM implementations suffer of severe limitations, stemming from the inherently restricted nature of the best-effort hardware mechanisms that they employ.

Such a design approach limits the applicability of HTM in a number of ways: not only it explicitly restricts the maximum amount of memory positions that can be accessed by transaction, but also makes hardware transactions unable to withstand events that lead to scratching the processor's cache, which includes, notably, system calls, context switches and interrupt requests (including periodic timer interrupts raised for OS scheduling purposes). Overall, these restrictions make current HTM systems unfit to serve as a general-purpose synchronization mechanism, significantly limiting the scope of their applicability.

This work aims at tackling precisely this issue by introducing *Speculative Read Write Lock* (SpRWLock), a novel HTM-based synchronization primitive that provides a key benefit: allowing read-only atomic blocks to execute outside the scope of any hardware transaction, thus, effectively sparing them from the inherent limitations affecting existing HTM implementations.

SpRWLock combines two key novel techniques aimed, respectively, at ensuring safety and at maximizing efficiency.

SpRWLock preserves safety of read-only atomic blocks, which run outside the scope of hardware transactions, by using a simple, yet surprisingly effective, technique: it requires update transactions, which execute using HTM, to check, at commit time, whether there are any active read-only atomic blocks, and allows them to commit only if none is found; forcing them to abort otherwise.

This technique can yield remarkable (up to  $6\times$ ) throughput gains over plain HTM in workloads that have long read-only atomic blocks. However, these throughput gains are achieved at the cost of an increased latency of update atomic blocks, which can suffer from frequent aborts (and theoretically from starvation) in read-dominated workloads.

SpRWLock addresses these shortcomings by complementing the above base algorithm with two ad-hoc scheduling schemes, which we refer to as reader synchronization and writer synchronization.

We evaluated SpRWLock via an extensive experimental study conducted using the HTM implementations available on Intel's Broadwell and IBM's Power8 CPUs and encompassing synthetic micro-benchmarks aimed at assessing the sensitivity of the proposed solution to a broad spectrum of workloads, as well as standard benchmarks (TPC-C, STMBench7) and real applications (KyotoDB). The results of our study shows SpRWLock can yield throughput gains of up  $15 \times$  with respect to both plain HTM -based solutions, as well as state of the art, non-speculative read-write lock implementations.

viii

# Keywords

transactional memory, concurrency control, read-write lock, lock elision, hardware

# Contents

| C             | ontents              |                                 |    |

|---------------|----------------------|---------------------------------|----|

| $\mathbf{Li}$ | st of                | Figures xi                      | ii |

| 1             | Inti                 | roduction                       | 1  |

| <b>2</b>      | $\operatorname{Rel}$ | ated Work                       | 7  |

|               | 2.1                  | Read Write Lock Implementations | 8  |

|               |                      | 2.1.1 Big Reader Lock           | 9  |

|               |                      | 2.1.2 PRWL                      | 9  |

|               |                      | 2.1.3 RCU                       | 9  |

|               | 2.2                  | Transactional Memory            | 10 |

|               | 2.3                  | Software Transactional Memory   | 12 |

|               |                      | 2.3.1 Transactional Locking II  | 13 |

|               |                      | 2.3.2 TinySTM                   | 13 |

|               |                      | 2.3.3 NOrec                     | 14 |

|               | 2.4                  | Hardware Transactional Memory   | 15 |

|               |                      | 2.4.1 zEC12                     | 16 |

|               |                      | 2.4.2 POWER8                    | 16 |

|               |                      | 2.4.3 TSX                       | 17 |

|               |                      | 2.4.4 HRWLE                     | 17 |

|               | 2.5                  | Lock Elision                    | 19 |

|    |            | 2.5.1          | Legacy Code                                   | 19               |

|----|------------|----------------|-----------------------------------------------|------------------|

|    | 2.6        | Hybrid         | d Transactional Memory                        | 20               |

|    |            | 2.6.1          | HyNOrec                                       | 20               |

|    |            | 2.6.2          | Invyswell                                     | 20               |

|    |            | 2.6.3          | PhaseTM and Split Hardware                    | 22               |

|    | 2.7        | Self T         | uning                                         | 23               |

|    |            | 2.7.1          | TinySTM                                       | 23               |

|    |            | 2.7.2          | TSX Tuning                                    | 24               |

|    |            | 2.7.3          | Green-CM                                      | 24               |

|    |            | 2.7.4          | Proteus TM                                    | 25               |

| 3  | <b>A</b> 1 |                |                                               | 27               |

| 3  | 3.1        | orithm<br>Base | l<br>Algorithm                                | <b>2</b> 7<br>28 |

|    | 3.1        |                |                                               | $\frac{20}{32}$  |

|    | 3.2        | 3.2.1          | uling Techniques       Reader Synchronization | 32               |

|    |            | 3.2.1          | v                                             | 32               |

|    | 0.0        | -              | Writer Synchronization                        |                  |

|    | 3.3        |                | ctness and Fairness                           | 36               |

|    | 3.4        | Optim          | nizations                                     | 38               |

| 4  | Eva        | luatio         | 1                                             | 41               |

|    | 4.1        | Sensit         | ivity Analysis                                | 42               |

|    |            | 4.1.1          | Impact of scheduling                          | 49               |

|    |            | 4.1.2          | Reader tracking scheme                        | 51               |

|    | 4.2        | STME           | Bench7                                        | 53               |

|    | 4.3        | TPC-0          | g                                             | 57               |

|    | 4.4        | Kyoto          | Cabinet                                       | 60               |

| 5  | Con        | clusio         | ns and Future Work                            | 63               |

|    | 5.1        | Future         | e Work                                        | 64               |

| Bi | ibliog     | graphy         |                                               | 65               |

# List of Figures

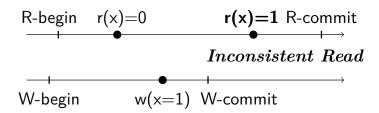

| 1.1 | Allowing a writer to commit while there is an active reader may lead to       |    |

|-----|-------------------------------------------------------------------------------|----|

|     | inconsistent snapshots                                                        | 4  |

| 3.1 | A read access during an active update transaction will abort the latter.      | 30 |

| 3.2 | A read access which commits before an active update transaction writes        |    |

|     | on shared values or verifies the state allows it to successfully commit.  .   | 30 |

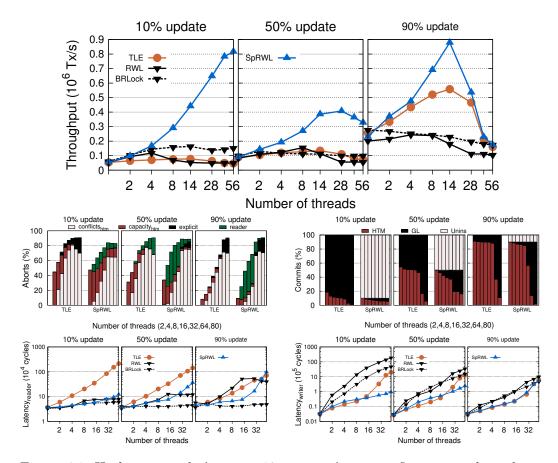

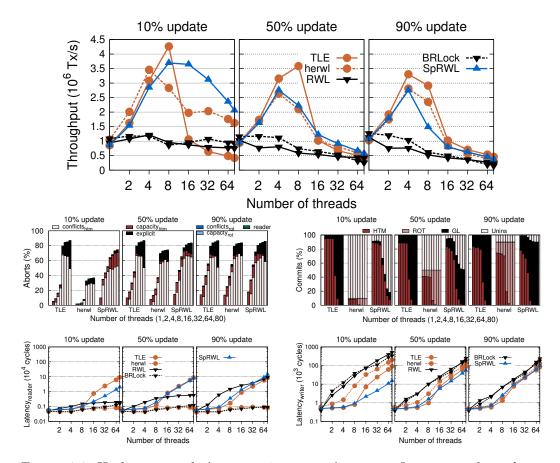

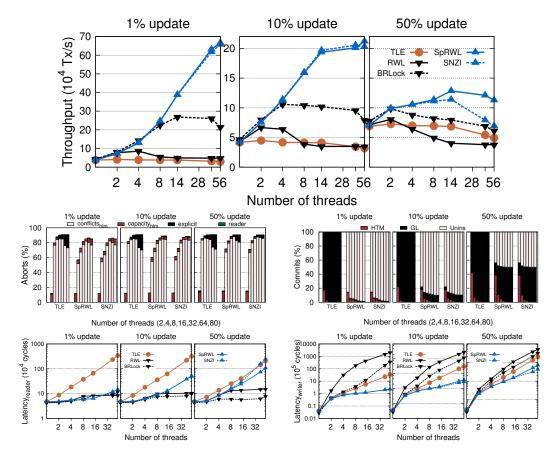

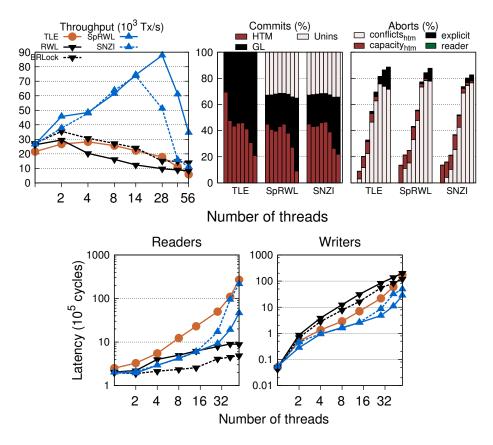

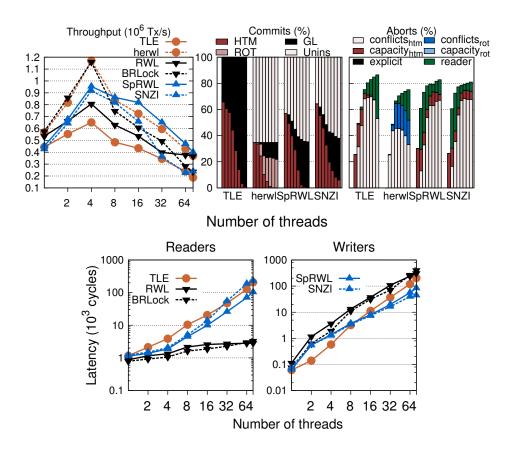

| 4.1 | Hashmap: reader's size = $10 \times$ writer's size configuration: throughput, |    |

|     | abort rate, and breakdown of commit modes at $10\%,\;50\%$ and $90\%$         |    |

|     | update ratios on Intel                                                        | 43 |

| 4.2 | Hashmap: reader's size = $10 \times$ writer's size configuration: throughput, |    |

|     | abort rate, and breakdown of commit modes at $10\%,\;50\%$ and $90\%$         |    |

|     | update ratios on POWER8                                                       | 44 |

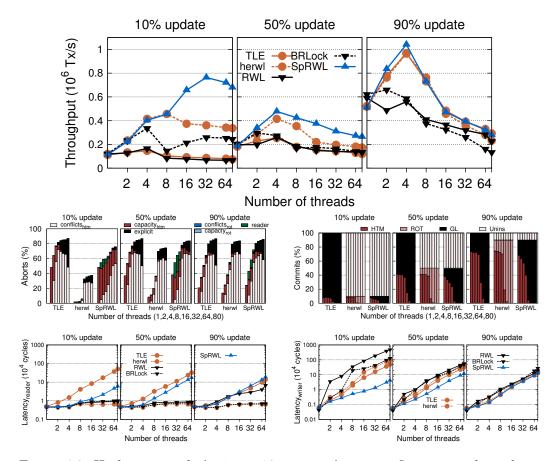

| 4.3 | Hashmap: reader's size = $1 \times$ writer's size configuration: throughput,  |    |

|     | abort rate, and breakdown of commit modes at $10\%,\;50\%$ and $90\%$         |    |

|     | update ratios on Intel                                                        | 45 |

| 4.4 | Hashmap: reader's size = $1 \times$ writer's size configuration: throughput,  |    |

|     | abort rate, and breakdown of commit modes at $10\%,\;50\%$ and $90\%$         |    |

|     | update ratios on POWER8                                                       | 46 |

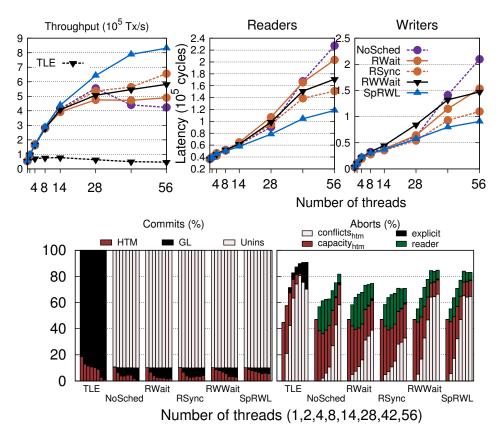

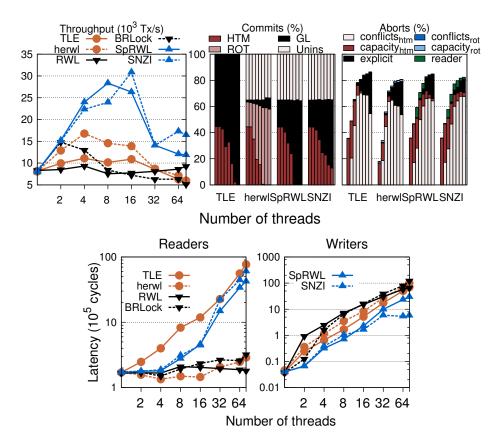

| 4.5 | SpRWLock variants: readers execute 10 lookups, writers execute 1 in-          |    |

|     | sert/delete. 50% update operations on Intel                                   | 49 |

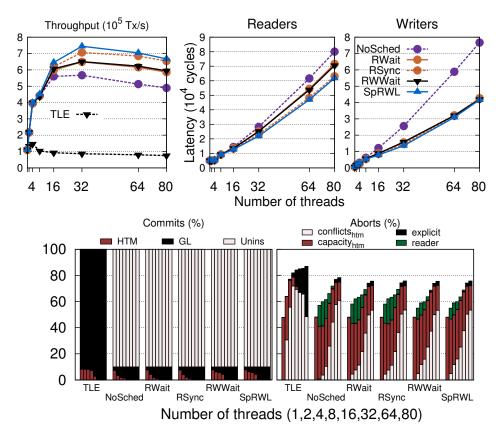

| 4.6  | SpRWLock variants: readers execute 10 lookups, writers execute 1 in-                                   |    |

|------|--------------------------------------------------------------------------------------------------------|----|

|      | sert/delete. 50% update operations on POWER8. $\ldots$                                                 | 50 |

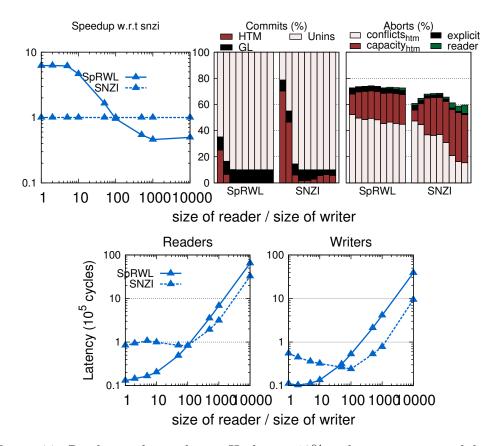

| 4.7  | Reader tracking scheme: Hashmap, $10\%$ update operations, while vary-                                 |    |

|      | ing the size of readers at 80 threads on POWER8                                                        | 52 |

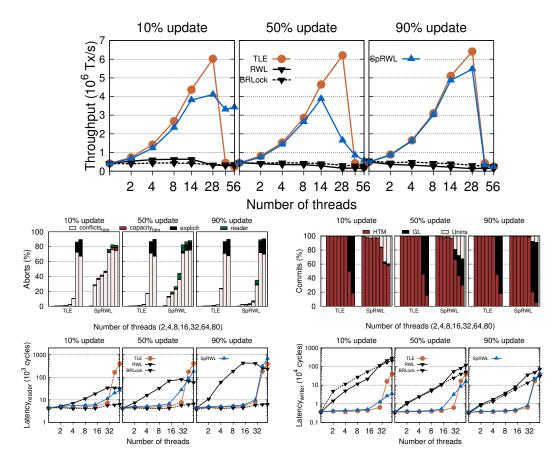

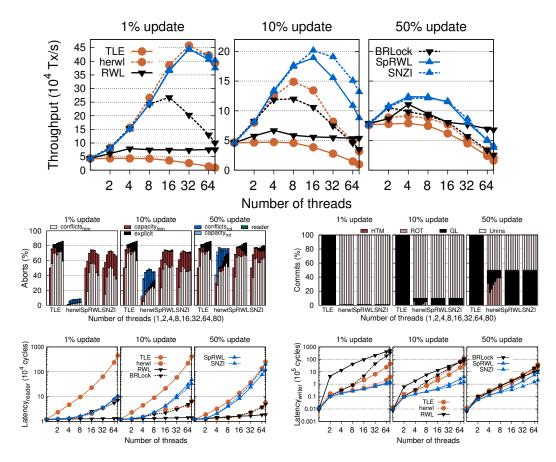

| 4.8  | STMBench7: throughput, abort rate, and breakdown of commit modes                                       |    |

|      | at 1%, 10% and 50% update ratios on Intel. $\ldots$ $\ldots$ $\ldots$ $\ldots$ $\ldots$                | 54 |

| 4.9  | STMBench7: throughput, abort rate, and breakdown of commit modes                                       |    |

|      | at 1%, 10% and 50% update ratios on POWER8                                                             | 55 |

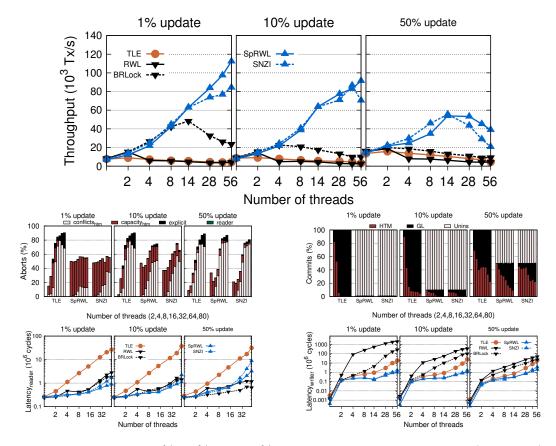

| 4.10 | TPC-C. 1%, 10%, and 50% update operations. Stock-level (read-only)                                     |    |

|      | and Payment (update) transaction profiles on Intel. $\ldots$                                           | 56 |

| 4.11 | TPC-C. 1%, 10%, and 50% update operations. Stock-level (read-only)                                     |    |

|      | and Payment (update) transaction profiles on POWER8. $\ldots$                                          | 57 |

| 4.12 | TPC-C. Mix comprising the following transaction profiles: Stock-level,                                 |    |

|      | 31%, Delivery, 4%, Order Status, 4%, Payment, 43%, and New Order,                                      |    |

|      | 18% on Intel $\ldots$ | 58 |

| 4.13 | TPC-C. Mix comprising the following transaction profiles: Stock-level,                                 |    |

|      | 31%, Delivery, 4%, Order Status, 4%, Payment, 43%, and New Order,                                      |    |

|      | 18% on Power8                                                                                          | 59 |

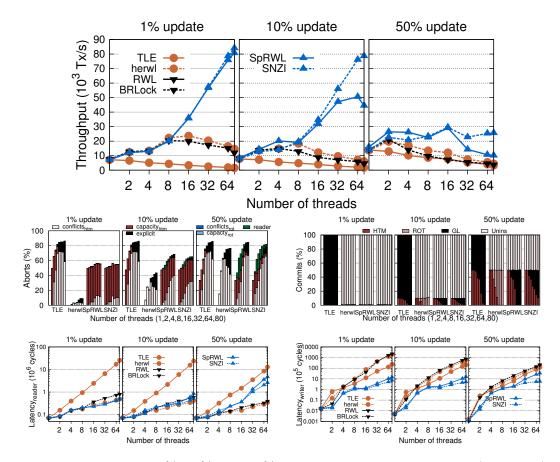

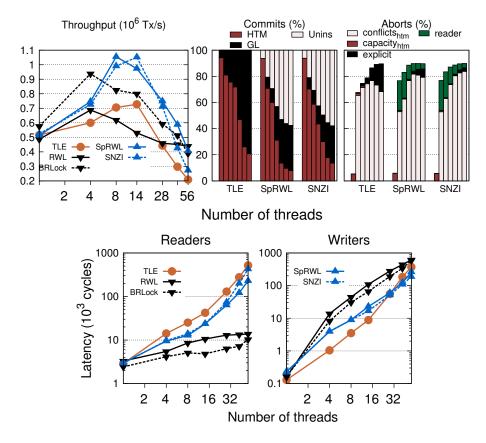

| 4.14 | Kyoto: throughput, abort rate, and breakdown of commit modes for the                                   |    |

|      | wicked benchmark on Intel                                                                              | 60 |

| 4.15 | Kyoto: throughput, abort rate, and breakdown of commit modes for the                                   |    |

|      | wicked benchmark on Power8                                                                             | 61 |

# List of Algorithms

| 1 | — Reader basic algorithm(thread $tid$ )            | 28 |

|---|----------------------------------------------------|----|

| 2 | — Writer basic algorithm (thread $tid$ )           | 29 |

| 3 | — Reader synchronization algorithm (thread $tid$ ) | 33 |

| 4 | — Writer synchronization algorithm (thread $tid$ ) | 35 |

# Glossary

- BFHW bloom filter-based hardware. 1, 21, 22

- BRLock Big Reader Lock. 1, 9, 48, 50, 51, 53, 55, 56

- CAM Content Addressable Memory. 1, 16

- **CF** Collaborative Filtering. 1, 25

- **CPU** Computer Processing Unit. 1

- HLE Hardware Lock Elision. 1, 17

- HRWLE Hardware Read-Write Lock Elision. iii, vii, 1, 17–19, 27, 41, 48, 50, 51

- HTM Hardware Transactional Memory. iii, vii, 1, 2, 15–20, 22, 23, 27, 60

- HyNOrec Hybrid No Ownership records. 1, 20

- HyTM Hybrid Transactional Memory. 1, 20, 22

- **IPI** Inter-Processor Interrupts. 1, 9

- IrrevSW irrevocable software. 1, 21, 22

- KPI Key Performance Indicator. 1, 25

- LE Lock Elision. 1

- LiteHW lightweight hardware. 1, 21, 22

#### GLOSSARY

xviii

- NOrec No Ownership records. 1, 14, 20

- **P8** POWER8. 1, 16–18

- PhTM Phased Transactional Memory. 1, 22

- **PRWL** Passive Reader-Writer Locks. 1, 9

- **RAM** Random Access Memory. 1

- ROT Rollback-Only Transactions. 1, 18, 19

- RTM Restricted Transactional Memory. 1, 17

- **RWL** Read/Writer Lock. 1, 8, 9, 17, 19, 41, 48, 50

- SGL Single Global Lock. 1, 2, 18, 19, 22

- SglSW single global lock software. 1, 21, 22

- **SLE** Speculative Lock Elision. 1, 17, 19

- **SpecSW** speculative Software. 1, 21, 22

- **SpRWLock** Speculative Read Write Lock. iii, vii, xi, xiii, 1, 3–5, 27–31, 33–35, 41–56, 59, 60

- STM Software Transactional Memory. 1, 2, 12–14, 20, 22, 23

- TL2 Transactional Locking II. 1, 13

- **TLE** Transactional Lock Elision. 1, 46, 47, 49, 50

- TM Transactional Memory. iii, vii, 1, 2, 10–12, 15, 19, 20, 23, 24, 27, 60

- TML Transactional Mutex Lock. 1, 14, 15, 20

- **TSC** Time Stamp Counter. 1

#### GLOSSARY

**TSX** Transactional Synchronization Extensions. 1, 17

**UCB** Upper Confidence Bound. 1, 24, 25

**zEC12** *IBMs zEnterprise EC12*. 1, 16

## Chapter 1

## Introduction

During various decades processors frequencies have been enjoying an exponential increase. Since early 2000, though, this trend stopped as manufacturers hit the so called "Power Wall": due to thermal issues, it is nowadays economically infeasible to further increase the operational frequencies of single core processors. This has brought a paradigm shift not only in the way hardware is designed, turning multi-core processors into a mainstream technology, but also in the way software is built - bringing parallel computing to the forefront of software development.

Unfortunately, developing parallel applications is well known to be a challenging task. One major source of parallel applications complexity is the implementation of a synchronized access to shared resources. Indeed, the classic approach to synchronization problems is to rely on a lock-based scheme, which are known as susceptible to several problems such as deadlocks, livelocks, priority inversions, etc. Given the increased relevance of parallel computing, over the last decade a large research effort has been devoted to identifying simpler, yet highly efficient, alternative synchronization paradigms.

Transactional Memory (TM) is probably one of the alternative synchronization methods to have been most intensively investigated as of late. Making use of Database Systems concept of Transactions, TM is an Automatic Mutual Exclusion method, where Programmers no longer need to worry with the synchronization, needing only to code which operations to execute concurrently. TM system would then ensure atomicity by detecting and resolving any conflict arising between concurrent transactions. The TM abstraction can be implemented in software, known as *Software Transactional Memory* (STM), hardware (*Hardware Transactional Memory* (HTM)) or combinations thereof.

Compared to other synchronization methods, HTM focuses on minimizing transaction overhead through hardware support, reducing or even removing the need of programming instrumentation on read and write accesses to shared resources. Various studies [1–6] have clearly shown that HTM can achieve, at least in certain workloads, impressive performance gains when compared to software based implementations. Unfortunately, though, existing HTM implementations also suffer of several relevant restrictions that can severely hamper its performance.

Indeed, even though existing HTM implementations come in different flavors [4, 7–9], they all share a key common treat: they all support transactions that perform a limited number of memory accesses. Whenever a transaction exceeds the maximum HTM capacity, it needs to be executed using a fall-back synchronization method, namely a *Single Global Lock* (SGL) that executes pessimistically and whose activation causes the immediate abort of any concurrent HTM transaction.

Such a design approach limits the applicability of HTM in a number of ways: not only it explicitly restricts the maximum amount of memory positions that can be accessed by transaction, but also makes hardware transactions unable to withstand events that lead to scratching the processor's cache, which includes, notably, system calls, context switches and interrupt requests (including periodic timer interrupts raised for OS scheduling purposes). Overall, these restrictions make current HTM systems unfit to serve as a general-purpose synchronization mechanism, significantly limiting the scope of their applicability.

This work aims at tackling precisely this issue by introducing *Speculative Read Write Lock* (SpRWLock), a novel HTM-based synchronization primitive that provides a key benefit: allowing read-only atomic blocks to execute outside the scope of any hardware transaction, thus, effectively sparing them from the inherent limitations affecting existing HTM implementations. SpRWLocks name stems from the fact that it exposes to programmers the familiar interface of a classic read-write lock and can, therefore, be seen as a specialized HTM-based technique for eliding this type of locks in legacy applications. However, SpRWLock can also be straightforwardly employed in applications that assume a transactional API by mapping the beginning of a read-only or an update transaction to a request for acquiring a read or write lock, respectively.

SpRWLock combines two key novel techniques aimed, respectively, at ensuring safety and at maximizing efficiency.

SpRWLock preserves safety of read-only atomic blocks, which run outside the scope of hardware transactions, by using a simple, yet surprisingly effective, technique: it requires update transactions, which execute using HTM, to check, at commit time, whether there are any active read-only atomic blocks, and allows them to commit only if none is found; forcing them to abort otherwise. The correctness of this approach hinges on two key properties of HTM:

- HTM externalizes the memory writes produced by an update transaction only if it successfully commits, making them visible to both transactional and nontransactional code atomically. This ensures that read-only atomic blocks never observe uncommitted (e.g., intermediate) writes of a concurrent update transaction.

- HTM detects conflicts between transactional and non-transactional code in an eager fashion, triggering the immediate abort of the former a property that is known as *strong isolation* in the literature [10]. This property avoids data races, which might otherwise occur if a read-only atomic block started, after its state was checked (and found inactive) by a concurrent update transaction. As illustrated in Fig. 1.1, if the update transaction was to be allowed to commit the read-only atomic block could observe an inconsistent snapshot, e.g., by returning different values upon two subsequent reads of the same memory

Figure 1.1: Allowing a writer to commit while there is an active reader may lead to inconsistent snapshots

position. SpRWLock prevents such a scenario by leveraging the strong isolation property of HTM, which ensures that if a read-atomic block alters its own state after it has been checked by a concurrent update transaction, then the latter will be immediately aborted.

As we will show, the technique described above can yield remarkable (up to  $6\times$ ) throughput gains over plain HTM in workloads that have long read-only atomic blocks. However, these throughput gains are achieved at the cost of an increased latency of update atomic blocks, which can suffer from frequent aborts (and theoretically from starvation) in read-dominated workloads.

SpRWLock addresses these shortcomings by complementing the above base algorithm with two ad-hoc scheduling schemes, which we refer to as reader synchronization and writer synchronization.

The reader synchronization scheme requires that read-only atomic blocks, before starting, wait for the completion of active concurrent update atomic blocks, if any. This technique not only reduces the likelihood for an update transaction to abort due to the existence of a concurrent read atomic block; it also guarantees an important fairness property for write atomic blocks, i.e., it ensures that if a write atomic block is activated before a read atomic block, then the former cannot be aborted by the latter. The reader synchronization scheme of SpRWLock is further enhanced by allowing read-only atomic blocks to shortcut their initial waiting phase in case they find some other read-only atomic block already waiting: in such a case, the last activated read-only atomic block joins the one already waiting and starts as one the latter does. This brings two advantages: reducing the average duration of the readers' waiting phase — and, hence, their latency — and striving to minimize the duration of time windows during which some reader is active by aligning their start time — which increases the chance for update atomic blocks to commit successfully.

The writer synchronization scheme aims, instead, at optimizing the scheduling decision on when to activate an update atomic block by pursuing a twofold goal: on one hand, postponing the activation of update atomic blocks in order to reduce the chances that they have to abort, eventually, due to a concurrent read atomic block; on the other hand, activating update atomic blocks as early as possible, to maximize concurrency already active read atomic blocks. This is achieved by estimating, at run-time, the average duration of atomic blocks, and accordingly delaying the activation of an update atomic block in order to maximize the chances that it requests to commit shortly after the last concurrent read atomic block completed.

We evaluated SpRWLock via an extensive experimental study conducted using the HTM implementations available on Intel's Broadwell [11] and IBM's Power8 [12] CPUs and encompassing synthetic micro-benchmarks aimed at assessing the sensitivity of the proposed solution to a broad spectrum of workloads, as well as standard benchmarks (TPC-C [13], STMBench7 [14]) and real applications (KyotoDB [15]). The results of our study shows SpRWLocks throughput can reach  $15 \times$  typical TM systems in some of the standard benchmarks, at the cost of reader latency.

## Chapter 2

## **Related Work**

With the emergence of multi-core architectures, the need for a synchronization method between parallel threads accessing shared resources has been a critical priority. In fact, the conventional synchronization approach based on locking is well known to suffer from several problems.

Coarse-grained locking, although easy to implement, is far too pessimistic as it can overly restrict parallelism, failing to take full advantage of modern multi-core systems. Fine-grained locking, although enabling good performance, is complex to implement correctly, debug and reason about [16]. Furthermore, it compromises a key desirable property of software: composability [16]. Using Locks as a synchronization method not only disables concurrent access to such values, but also delays the threads themselves with its additional overhead during its normal workloads.

A transaction, as a concept, was first developed for databases, as a set of operations that manipulate data atomically. The main purpose was to keep the database consistent, while allowing the concurrent access to the database. In order to achieve this, transactions have to be Atomic, Consistent, Isolated and Durable (ACID).

These features are also essential for parallel programming. Atomicity requires that changes done within a transaction appear as all or none to other code. Consistency demands that as data changes the database always remains in a valid state. Isolation ensures that all changes done from within a transaction must remain invisible to all other transactions. Durable as in case of failure the system can either recover entirely or discard the changes committed by the failing transactions.

### 2.1 Read Write Lock Implementations

First described by Courtois et al. [17], the *Read/Writer Lock* (RWL) abstraction allows multiple readers to access the same value simultaneously, but locking the object from both readers and writers when a writer requests access to the value. Classic implementations of the RWL abstraction rely internally on mutex locks and semaphores.

The basic algorithm consists of two semaphores, one for active readers and one for writers. The reader, upon start, increments a waiting list to inform it is currently waiting to activate. It then verifies there are no writers active by checking the writer lock. If a writer is active, the reader will wait until the writer finishes. The reader then increments the semaphore and removes itself from the waiting list. After performing the critical section, the reader removes itself from the semaphore allowing writers to run again.

The writer begins by also publishing itself in a waiting list to inform it is ready to begin. It then verifies no reader is active and, if so, attempts to acquire the writer lock. If successful it removes itself from the waiting list. Upon conclusion it removes itself from the writing lock, first signaling readers they may begin and afterwards writers.

The overall concurrent accesses allowed by this typical RWL can be seen in 2.1. In order to ensure a thread-safe access to the waiting lists a mutex lock is used.

The key challenge of RWLs design is how to minimize the additional overheads incurred with respect to plain mutex locks, while ensuring fair access to the lock to both readers and writers.

The main drawback of RWL is their poor scalability as they only have concurrency in reader-reader interactions as shown in table 2.1.

#### 2.1. READ WRITE LOCK IMPLEMENTATIONS

|        | Reader | Writer |

|--------|--------|--------|

| Reader | Yes    | No     |

| Writer | No     | No     |

Table 2.1: Concurrent accesses allowed by typical RWL

#### 2.1.1 Big Reader Lock

*Big Reader Lock* (BRLock)s [18] objective is to allow read-only transactions to function as fast as possible by locking a CPU-local spinlock. This implies a array of locks is created, one for each CPU. This algorithm was developed for read intensive workloads, as its objective is to increase reader throughput, resulting however in the reduction of writers throughput. The loss of writer throughput is due to the need of writers acquiring the full lock array to function.

#### 2.1.2 PRWL

*Passive Reader-Writer Locks* (PRWL) developed by Liu et al. [19], focuses in several points:

- 1. Readers do not need to share data between them, as such there is no shared state or the need of memory barriers if no writer exists.

- 2. In typical RWL writer use memory barriers to ensure version updates are visible to all readers/writers. To solve this situation without costly memory barriers PRWL uses *Inter-Processor Interrupts* (IPI) a special type of interrupt where one processor interrupts another, to force staggered readers to check the snapshot update.

### 2.1.3 RCU

Read-Copy-Update (RCU) [20] is an alternative synchronization mechanism that targets read-dominated workloads. Unlike RWLs, with RCU, a read-only critical section does not need to acquire any mutex, it just flags itself, using a memory barrier, at the beginning and end of critical section. To ensure correctness, a writer modifying shared data, would create a copy of the data and apply the modifications to the copy. Readers that existed prior to the write would continue to access the older, unmodified data, while new readers get to witness the updates. Only when all readers that existed before the writer have completed their critical sections, the unmodified data is replaced by the copy.

## 2.2 Transactional Memory

TM borrows the abstraction of transactions from databases to the parallel programming domain. It provides programmers with the ability to execute transactions on shared memory data. These transactions are either committed by TM (i.e., the changes of the transaction are applied atomically to the data) or aborted (i.e., the changes are discarded as if they never happened) complying with ACID.

TM is a parallel programming paradigm that avoids the pitfalls of traditional locking techniques while promising the performance of fine-grained locking [16]. Programmers using TM need only to worry on their applications logic, not on how to implement synchronization, thus easing the development of concurrent applications that are both scalable and thread-safe in parallel computing.

TM algorithms can be classified according to *data versioning*, *conflict detection*, *granularity* and *read visibility*.

- Data versioning has the objective of guaranteeing consistency among all reads and writes. It is implemented in several different methods with its objective being to guarantee all transactions work on a consistent snapshot of the systems memory. TM are mainly divided into *eager versioning* and *lazy versioning*.

- lazy versioning stores all memory changes the transaction implements in a buffer to insert in the shared memory on commit. If the transaction is successful the new values are copied to the memory, which results in a

small delay as all values are copied. If however the transaction is aborted no further operations are necessary as the values were never written in the system.

- In eager versioning however the transaction writes its new values directly in memory, storing the old value in a log for its possible abort. This allows its commit to be much faster, however if the transaction is aborted it must recover all overwritten values causing some additional delay in conflicting transactions.

- Conflict Detection is needed when two of more transactions access the same value and at least one of them changes the value before all other transactions sharing access commit. To resolve these situations all reads and writes are tracked and checked for collisions in one of two ways: *pessimistic conflict detection* and *optimistic conflict detection*.

- With *pessimistic conflict detection* the system eagerly checks the transactions accessed values. This allows for a quick conflict detection at the cost of performance due to its constant checks.

- optimistic conflict detection assumes a conflict will not occur in a transaction, checking all values before commit, thus avoiding the performance loss that *pessimistic conflict detection* has due to constant conflict checking. However this detection has the downside that conflicts are only detected at the very end, possibly delaying the abortion for a long time and wasting resources in an aborting transaction.

- Granularity is the level at which the TM detects conflicts. Granularity is generally either word-based, object-based, value-based or cache-line based. Wordbased granularity means that the TM system detects conflicts between 4 or

8 bytes. *Object-based*, as the name implies, means the system only checks each objects atomicity, leading to possible false conflicts of different variables inside an object. *Value-based* the system locally stores read addresses and values, allowing the transaction to later confirm the new and previous value are the same. Finally *cache-line based* is a *hardware* specific granularity explained further on.

• *Read Visibility* can be divided in *visible*, where reader inform which memories they have accessed increasing memory checks and *invisible*, where readers do not inform other active transactions of which shared memories they read, forcing writers to check if reads and writes are complete and a consistent snapshot of the system is maintained on commit.

## 2.3 Software Transactional Memory

Due to the difficulty of manufacturing and testing hardware based TM solutions, STM was developed to implement TM only as a software framework, enabling portability across different hardwares.

STM relies on instrumented read and write accesses to shared memory locations from transactional blocks. This instrumentation then allows the software to detect conflicts through *data versioning* and *conflict detection* as previously mentioned. This generates a higher overhead compared to the *hardware-based* alternative. On the other hand one of its main advantages is the transaction size it can support, unlike *hardware-based* solutions.

Due to the low cost and high flexibility of software implementations, many different designs of STM were developed. STM can be divided according to the previous categories. Table 2.2 shows some popular and efficient STM implementations.

#### 2.3. SOFTWARE TRANSACTIONAL MEMORY

|              | Data Versioning | Conflict Detection | Granularity |

|--------------|-----------------|--------------------|-------------|

| TL2 [21]     | Lazy            | Optimistic         | Word/Object |

| TinySTM [22] | Lazy/Eager      | Pessimistic        | Word        |

| NORec $[23]$ | Lazy            | Pessimistic        | Value       |

Table 2.2: Popular STM characteristics

#### 2.3.1 Transactional Locking II

Transactional Locking II (TL2), proposed by Dave Dice et al. [21], works as a twophase locking scheme, maintaining a global version clock, which is incremented by all writing transactions, and versioned write-locks for every shared memory location. It works with optimistic conflict detection and lazy versioning.

On start all transactions read and store the current global version clock in a local variable to identify its read-version number. The transaction then runs the user transactional code locally, maintaining a list of versioned write-locks of all read values (read-set) and written values (write-set). The transaction also verifies in each read value that its current version is  $\leq$  read-version number and the read values lock is free to guarantee that the value has not been modified since the transaction began. When it finishes the writer acquires the write-set locks using a bounded spinning (aborting after a fixed period of unsuccessfully acquiring a lock). It then performs a increment-and-fetch operation of the global version clock recording its value in a local write-version variable. Finally it re-validates the read-set  $\leq$  read-version number to guarantee no accessed memory locations were modified during the transaction. If in both checks a value is locked or its value does not comply to the rules above then the transaction aborts.

#### 2.3.2 TinySTM

Pascal et al. later proposed *TinySTM* [22], a word-based variant of LSA [24]. *TinySTM*, like TL2 uses both *global version clock* for snapshot consistency and *versioned write-locks* for shared memory addresses. However, instead of locking all needed writes just before commit the algorithm acquires locks on read. *TinySTM*  works with *pessimistic conflict detection* and is presented as able to use both *versioning* methods.

Read-only transactions are benefited in this algorithm, the reader verifies the shared memories lock is free, reads the corresponding value and then checks the lock again to confirm that no changes occurred in the meantime. A reader may need to extend its snapshot in case it is reading a value that has a version number greater than the transactions. This is done by validating the read-set and making sure they have not been updated meanwhile.

Write transactions acquire the lock to guarantee that there are no concurrent writers. If the lock bit is set the writer verifies its the current lock owner, otherwise waits or aborts. In the presented *TinySTM* transactions are set to abort immediately. This is useful in workloads with high contention as it minimizes the amount of useless work done.

*TinySTM*, as mentioned above, can use both *eager versioning*, with *write-through*, resulting in a smaller overhead and delay for other transactions on successful commit, or *lazy versioning* with *write-back*, resulting in a larger overhead in all transactions but smaller delay on abort.

It also presents the concept of *Hierarchical locking*, a strategy to reduce the validation cost of read-sets by reducing the number of read locks while avoiding the increase of aborts due to shared memory with the same lock. *Hierarchical locking* is specially useful if transactions read many memory locations and there are few competing write transactions.

### 2.3.3 NOrec

No Ownership records (NOrec) presented by Luke Dalessandro et al. [23] is a highly scalable STM on read-mostly workloads, allowing any reader to promote into a writer at anytime limiting however the algorithm to a single write transaction system-wide. NOrec uses *lazy versioning* and *pessimistic conflict detection*.

NOrec minimizes its overhead by using Transactional Mutex Lock (TML), a

global clock counter, which allows writers to be serialized. By using TML readers only store a snapshot of the TML and a read-set, consisting of both read values and their addresses. On commit the reader checks its stored TML value and current TML value. If the value is the same then it finishes committing successfully. If the value is different, the reader needs to perform a validation of its read-set, checking its stored reads and current values to confirm its read-set is consistent.

Writer transactions buffer all their writes into a log, attempting to acquire the lock only on commit. This reduces the time TML is held by a transaction, allowing read-only transactions to commit more easily.

### 2.4 Hardware Transactional Memory

TM was initially proposed as a hardware based solution with the goal of "a new multiprocessor architecture intended to make lock-free synchronization as efficient (and easy to use) as conventional techniques based on mutual exclusion." [25].

After two decades of thorough TM research, it finally made to commercial hardware under the name *Hardware Transactional Memory* (HTM). All HTM systems provide the following machine instructions: begin, end and abort transactions.

- *Begin* instruction is used by the programmer to inform the HTM that a transaction has begun and all following reads and writes must be executed with atomicity and isolation guarantees.

- *End* instruction is called by the transaction to inform the TM that it is ready to commit.

- *Abort* instruction is used to abort a running transaction and call the abort handler, which is also activated upon a hardware triggered abort.

HTM detects conflicts with the granularity of a cache line, this differs from one processor to another. Table 2.3 shows the values for different processors that support HTM.

Table 2.3: HTM implementations of zEC12, Intel Core i7-4770 and POWER8. Adapted from [5]

| Processor Type                 | zEC12     | Intel Core i7-4770 | POWER8    |

|--------------------------------|-----------|--------------------|-----------|

| Conflict-detection granularity | 256 bytes | 64 bytes           | 128 bytes |

| Transactional-Load Capacity    | 1 MB      | 4 MB               | 8 KB      |

| Transactional-Store Capacity   | 8 KB      | 22 KB              | 8 KB      |

Although there exist different implementations of HTM, Nakaike et al. [5] show that no HTM outperforms all other for all workloads.

#### 2.4.1 zEC12

*IBMs zEnterprise EC12* (zEC12) [7] was the first commercial server to implement HTM. zEC12 uses L1 cache for conflict detection [26]. It provides *constrained transactions*, which are transactions guaranteed to eventually commit, avoiding the need of abort handlers. This characteristic allows zEC12 to perform well in highly contended scenarios [26].

#### 2.4.2 POWER8

*POWER8* (P8), also developed by *IBM* [27] uses *Content Addressable Memory* (CAM), a special type of memory, which keeps track of the address of cache lines accessed from within a transaction. CAM records all reads and writes, allowing for a quick search of all transactions using the searched word. Another characteristic of P8 is its *suspend and resume transactions*. These allow the programmer a higher layer of liberty compared to other HTM since it allows the system to *suspend* the transaction. During suspend no data accesses are recorded by the HTM allowing the user to access clocks and counters outside its isolation ie. updating values visible to other transactions. The main downside of P8 is its low capacity compared to other HTM, as shown in the table 2.3.

### 2.4.3 TSX

Intels Transactional Synchronization Extensions (TSX) [28] provides two programming interfaces: Hardware Lock Elision (HLE) and Restricted Transactional Memory (RTM).

RTM is a simple HTM interface which allows programmers to specify a fall-back code if the HTM cannot successfully execute.

HLE Hardware Lock Elision (HLE) is an interface that implements *Speculative Lock Elision* (SLE). Basically, it provides the ability of transparently replacing the legacy lock acquire and release instructions with *XACQUIRE* and *XRELEASE* instructions. This transforms critical sections protected by locks into transactions that are executed speculatively. HLE is backward compatible, i.e., code developed with HLE will work on hardware without TSX support by falling back to pessimistic execution. HLEs drawback is its incapability of setting a custom fall-back code, using the original locks in case of failure.

Another drawback both Intel interfaces suffer of is the possibility of *spurious-aborts* due to data-conflict caused by pre-fetching cache-lines [5]. Although Intels pre-fetching feature can be disabled, doing so can degrade performance of other applications.

### 2.4.4 HRWLE

Proposed by Felber et al. [29], *Hardware Read-Write Lock Elision* (HRWLE) is an algorithm, optimized for heavy-read workloads, which makes use of HTM concurrency capability to allow multiple writers to work concurrently via *hardware speculation*, enabling a different approach to the typical RWL system which only allows readers to run concurrently. For this HRWLE makes use of P8s previously presented characteristic, *suspend and resume transactions*.

HRWLE works by treating readers and writers in distinct ways: writers are

executed in HTM, allowing the system to automatically track conflicts between them. Conversely readers execute without any hardware instrumentation, hence avoiding the capacity limitations, which writers, by running in HTM, are subject to. Analogously to *BRLock*, in HRWLE readers announce their presence by flagging their presence in a thread-local variable (and ensuring the visibility of this update via a memory barrier).

To ensure correctness, no readers can be active during a writer commit. HTM however is known for its strong isolation, forcing the abortion in case of any data conflicts, such as flag verifications.

Because of this isolation, in order to allow writers to commit more easily the algorithm makes use of P8s *suspend and resume* feature to *suspend* their transaction right before commit. The writer can then access each readers flag to wait for each active reader to commit without aborting, maintaining a consistent snapshot and avoiding the writers abort due to flag value changes. After confirming each previously active reader has finished, the writer commits.

As mentioned before, previously active readers are given priority in order to avoid starvation. Unfortunately, due to the HTMs strong isolation, writers cannot be given priority as any readers that access their data force an abort of the conflicting writer. HRWLE presents two methods of avoiding writer starvation: *Non-Speculative Transactions* and *Rollback-Only Transactions* (ROT).

If a writer has not successfully committed after a defined number of attempts, the algorithm tries to run it in ROT, a special HTM with minimized overhead. In this type of transaction the writer acquires SGL in *ROT-lock* mode, allowing only writers to execute concurrently. As it uses a minimized overhead, ROT transactions perform faster then HTM.

*Non-Speculative Transactions* is used by HRWLE when a transaction exceeds HTMs capacity or exceeds its maximum amount of tries defined in the configuration. In this case the writer acquires the SGL, waits for previous transactions to finish, performs its critical section and frees the lock afterwards. As the name implies, no other transaction may run during its execution.

Overall, HRWLE excels in workloads with high-capacity compared to the base HTM due to its fall-back paths. It also performs very well in high-contention workloads, compared to other RWL and HTM, as readers are un-instrumented and, in case of fall-back, ROT forces writer serialization, reducing SGL contention.

## 2.5 Lock Elision

Speculative Lock Elision(SLE), proposed by Rajwar et al. [30] is a novel technique which intends to dynamically spot and remove unnecessary serialization through locks, allowing previously locked critical sections to run concurrently. The concept of this paper is that frequent serialization lowers the performance of multi-threaded application, even if fine tuned. The main idea is that Hardware will dynamically identify synchronization operations, namely locks, and elide them, that is, instead of acquiring the lock the critical operation is executed as is. In the situation that two critical sections develop a conflict, the algorithm will fall-back to acquiring the lock pessimistically.

### 2.5.1 Legacy Code

Ruan et al. in their paper [31] make use of SLE as a way to allow legacy programs, previously implemented with lock-based synchronization, to elide the locks and implement the corresponding critical section as a transaction. They tested this implementation by changing the Compilers *cache\_lock and stats\_lock* instructions for atomic operations in TM. This allows legacy programs with limited performance in concurrency to be able to run in HTM without the programmers having to consider the new complexity of perform changes to their code.

## 2.6 Hybrid Transactional Memory

Given the restrictions of existing HTM implementations, researchers have investigated an alternative approach, which goes under the name of *Hybrid Transactional Memory* (HyTM). In HyTM systems, transactions are first executed using HTM, yet fall-back to a STM if necessary, in an attempt to make the best use of both implementations. Unfortunately the simultaneous execution of HTM and STM induce high overheads to assure their correct synchronization [1].

## 2.6.1 HyNOrec

Hybrid No Ownership records (HyNOrec), developed by Luke Dalessandro et al. [32], was created with the purpose of supporting concurrent hardware and software transactions while avoiding heavy instrumentation in hardware transactions. It uses lazy subscription and eager conflict detection.

As its name suggests, HyNOrec uses NOrec as its STM fall-back [23] which only requires a global clock, called TML. This allows for both HTM and STM to operate concurrently since both TM access and update this clock when writing.

Hardware Write transactions begin by reading TML to ensure they are subscribed to STM commit notifications, and increment it upon commit to signal software transactions. To avoid hardware-hardware conflicts due to TML changes, each processor core has its own local counter which each hardware transaction locally increments. This ensures a consistent snapshot, however it requires STM to increase its overhead as it must check the TML and each counter to guarantee its consistency with the HTM.

### 2.6.2 Invyswell

Proposed by Irina Calciu et al. [33], *Invyswell* Invyswell is a HyTM that relies on a modified Inval-STM as the fall-back path of HTM. *Invyswell* uses *lazy subscription* and *commit-time invalidation*.

Inval-STM uses a novel method of validation called *commit-time invalidation* an *optimistic conflict detection* where each transaction stores its read and writesets. During commit, the writer invalidates all conflicting transactions, giving itself priority. After finishing its *validation* it commits its changes to memory.

This simplifies the validation of other transactions, as they are immediately invalidated as if using *pessimistic conflict detection* without the regular conflict verification associated to this method.

To ensure its guarantees and increase the set of workloads where *Invyswell* performs well, five types of transaction were developed: *lightweight hardware* (LiteHW), *bloom filter-based hardware* (BFHW), *irrevocable software* (IrrevSW), *speculative Software* (SpecSW) and *single global lock software* (SglSW).

- LiteHW is a simple hardware transaction with no read or write software instrumentation. This allows for a faster execution. This benefit of LiteHW is also its downside as it is incapable of executing concurrently with software transactions.

- BFHW records its reads and writes, storing their memory location in Bloom filters. When finished, BFHW checks if the commit lock is free. If so, it increments the *hardware post commit lock* and commits. This lock prevents SpecSW from performing operations until it is free, allowing the BFHW to perform *commit-time invalidation*, with its recorded reads and writes, successfully.

- SpecSW is identical to *Inval-STM*. As with BFHW, SpecSW keeps track of accessed memory locations, both reads and writes, through Bloom filters. At commit time SpecSW performs *commit-time invalidation* with other SpecSW. Its main difference from *Inval-STM* is that it commits changes to memory be-

fore invalidating conflicting transactions.

- SglSW is a final transaction type used for small transactions the HTM does not support. Due to its small overhead SglSW is fast but does not allow for concurrent software executions as it acquires the SGL. It can however run in concurrency with HTM if it commits before BFHW and LiteHW check the SGL, as the HTM strong isolation detects and aborts if a data conflict occurs.

- IrrevSW is implemented for transactions that repeatedly could not commit in BFHW. As with SglSW it acquires the lock on start. All of its operations are immediately written to memory. During the execution of an IrrevSW, Spec-SWs are disallowed to commit and BFHWs must check if they are conflicting and abort if needed.

*Invyswell* first tries transactions using HTM, running either in LiteHW or BFHW depending on other active transactions and the expected size of the transaction. If a transaction is not supported in HTM, it is immediately executed in SglSW. If the number of attempts a hardware transaction tries exceeds the defined retry policy, the transaction is tried in SpecSW. Finally if SpecSW continues to abort it is escalated to IrrevSW.

### 2.6.3 PhaseTM and Split Hardware

Although not HyTM, *Phased Transactional Memory* (PhTM) [34] and *Split Hard-ware*(SplitTM) [35] use both HTM and STM. PhTM focuses on supporting several *phases* of the system, in which different TM-based synchronization schemes are used. It was presented with the following modes: Hardware, Software, Hybrid, Sequential and Sequential-NoAbort. This allows for adapting the employed TM implementation to the characteristics of the current workload. However, phase transitions take

a stop the world approach: all threads must complete executing using the current synchronization mechanism, before they are allowed to start the new phase and use a different synchronization scheme.

SplitTM uses both STM and HTM by splitting an STM into multiple HTM segments, overcoming current HTM nesting issues. SplitTMs HTM sub-transactions write to a thread-local log allowing the HTM to commit at any point of the parent transaction while ensuring isolation. HTMs also log their reads, allowing the parent transaction to maintain consistency as it can detect conflicts after the hardware transactions, where the reads occurred, have committed. Finally, on commit the parent transaction runs a hardware sub-transaction which writes all changes from the local write log to the main memory. Although allowing bigger transactions to be implemented in HTM, this implementations comes at the cost of instrumenting HTM transactions, tracking both reads and writes each HTM performs.

## 2.7 Self Tuning

As seen through the previous topics, TMs can be implemented in a variety of ways, each with their own set of parameters. These parameters are generally tuned manually, a time consuming and error prone task. Furthermore, it is not possible to implement a perfectly optimal configuration through a static manual tuning as workloads can vary over time. This motivated the investigation of self-tuning techniques for TM, of which I overview the following.

### 2.7.1 TinySTM

When proposing *TinySTM* [22] Felber et al. noticed that some parameters of their algorithm, such as *hierarchical locking*, had to be fine tuned to each workload. In order to allow their algorithm to perform well in a larger set of workloads, they developed a *hill-climbing* tuning algorithm. Starting with a certain number of locks, the tuner periodically adapted these parameters attempting to acquire a more optimal

value. This tuning algorithm proved capable of autonomously reaching throughput values close to those obtained by the team through static testing, optimized to the workload.

## 2.7.2 TSX Tuning

Diegues and Romano [8] tackled the problem of automatically identifying the optimal number of times a transaction should be attempted in hardware, and how to react to capacity aborts, by activating the fall-back immediately or treating it as a conflict induced abort. The two sub-problems are tackled using different selftuning algorithms, namely *hill-climbing* (with probabilistic jumps to avoid being trapped in local minimums) and *Upper Confidence Bound* (UCB) [36], a reinforcement learning algorithm that seeks an optimal trade-off between exploration of new configuration and exploitation of available knowledge. Its results showed that, as in *TinySTM*, self-tuning can reach results very close to those obtained through extensive off-line testing.

### 2.7.3 Green-CM

Proposed by Shady et al. Green-CM [37] focuses on a Contention Manager directed mostly to optimize energy consumption, that is, avoiding aborts and implementing low consumption sleeps so as to reduce the energy consumption of the TM. For this Green-CM proposes an energy efficient alternative for longer waits when blocked by a conflicting transaction. It separates waiting transactions into two types, long waits where they apply a time-based sleep, lowering consumption but also wait accuracy, and short waits were the algorithm applies a spin-based wait, a high energy consumption wait with high accuracy. To decide which back-off policy it should use, Green-CM makes use of both UCB and hill-climbing. Like TSX Tuning, Green-CM makes use of hill-climbing to explore the parameters searching for optimal configurations to the current workload. A problem of this method is that *hill climbing* continues to search for a better value even after arriving at the optimal configuration. In order to avoid changing to a less ideal configuration in subsequent oscillations, *Green-CM* uses a variant named *stabilizing* which functions as an UCB for the algorithm to avoid oscillating unnecessarily.

### 2.7.4 Proteus TM

Didona et al. proposed *Proteus TM* [38], a self-tuning algorithm that focuses on adapting multiple parameters for optimal configurations. *Proteus TM* makes use of *Collaborative Filtering* (CF), a prominent technique in *Recommender Systems*, which attempts to obtain the best value for a user-defined *Key Performance Indicator* (KPI) and *Bayesian optimization* to profile the current workload to use CF with. KPI infers the ideal configuration of new workloads based on previously discovered optimal configurations for other workloads, as such, the algorithm is first implemented with an off-line profile of optimal configurations for a set of workloads. It then builds a matrix with the parameters to optimize in order to apply CF. Finally whenever a new workload appears, *Proteus TM* first attempts to profile the workload based on stored optimal configurations, using *Bayesian optimization*, and recommending the resulting KPI maxed configuration for the workload.

## Chapter 3

# Algorithm

This chapter presents *Speculative Read Write Lock* (SpRWLock), a novel HTMbased techniques for eliding read-write lock, which, analogously to HRWLE, supports the concurrent execution of un-instrumented readers âĂŤ hence sparing them from HTMâĂŹs capacity limitations âĂŤ as well of writers using HTM. The key novelty of SpRWLock is that, unlike HRWLE, it does not rely on special hardware features (e.g., suspend-resume) available only on POWER8 processors by IBM, but assume that the underlying HTM implementation assumes a basic/conventional API for transaction demarcation and, as such, is a generic solution that can be adopted on any HTM system.

As already mentioned, SpRWLock exposes a classic read-write lock interface. As such, SpRWLock can be used as a drop-in, speculative replacement for conventional read-write locks in applications that already use this synchronization primitive; however, it is straightforward to adapt SpRWLock's algorithm to be employed also by TM-based applications, by mapping the begin and commit of read-only and update transactions to lock and unlock requests to a single global lock implemented using SpRWLock.

For the sake of clarity, we present SpRWLock in an incremental fashion. We start by presenting, in Section 3.1 a simple, base algorithm that embodies one of the key ideas at the basis of SpRWLock: enabling safe concurrency between un-

1: Gobal variables:  $state[N] \leftarrow \{\bot, \bot, \ldots, \bot\}$  $\triangleright$  One status per thread 2: 3: gl $\triangleright$  global lock for HTM fallback 4: function SpRWL\_READ\_LOCK  $state[tid] \leftarrow \texttt{#READER}$  $\triangleright$  Flag active reader 5:  $\triangleright$  Make sure writers see reader 6: MEM FENCE 7:READER GL SYNC() 8: end function 9: function SPRWL READ UNLOCK  $state[tid] \leftarrow \bot$  $\triangleright$  Exit critical section 10:11: end function 12: function READER GL SYNC if locked(ql) then 13: $state[tid] \leftarrow \bot$  $\triangleright$  Defer to gl writer 14: repeat until !locked(gl) $\triangleright$  wait until lock is free 15:go to 5 16:17: end function

**Algorithm 1** — Reader basic algorithm (thread tid)

instrumented readers and HTM-backed writers. We then extend this base algorithm in Section 3.2, by introducing two scheduling techniques that aim both at enhancing performance and ensuring fairness. We conclude by discussing the correctness of the proposed solution (Section 3.3) and presenting a set of relevant optimizations (Section 3.4).

## 3.1 Base Algorithm

The pseudo-code of SpRWLock base algorithm SpRWLock is reported in two parts: (i) the reader part 1 and (ii) the writer part 2. In the following, for brevity, we will refer to the threads that request to acquire the lock in read/write mode as readers/writers, respectively.

As already mentioned, write critical sections are executed speculatively, using HTM: a write lock acquisition request triggers the activation of a HTM transaction and the corresponding unlock request triggers the commit of its associated hard-ware transaction. Readers, conversely, are executed un-instrumented, i.e., without recurring to HTM, and are therefore spared from HTM's inherent limitations.

In order to ensure the safety of readers, in presence of concurrent writers exe-

Algorithm 2 — Writer basic algorithm(thread *tid*)

```

1: Gobal variables:

state[N] \leftarrow \{\bot, \bot, \ldots, \bot\}

2:

\triangleright One status per thread

3:

gl

\triangleright global lock for HTM fallback

4: function SpRWL_write_lock

attempts \leftarrow 0

5:

state[tid] \gets \texttt{\#HTM\_WRITER}

6:

BEGIN_HTM()

7:

\triangleright Start transaction

8: end function

9: function SPRWL WRITE UNLOCK

if state[tid] is #HTM_WRITER then

10:

11:

CHECK_FOR_READERS()

\triangleright Abort if there are active readers

\triangleright Write back updates

12:

TX COMMIT

else

13:

14:

RELEASE GL()

15: end function

16: function BEGIN_HTM

repeat until !locked(gl)

\triangleright wait until lock is free

17:

18:

attempts + +

status \leftarrow TX\_BEGIN()

\triangleright Begin HTM transaction

19:

if status is SUCCESS then

20:

\triangleright Add lock to read-set and...

if locked(gl) then

21:

\triangleright abort Tx if lock is busy

22:

TX_ABORT()

23:

else

24:

ABORT_HANDLER()

25: end function

26: function Abort_Handler

if attempts > MAX\_RETRIES then

\triangleright is budget over?

27:

state[tid] \leftarrow \texttt{#GL_WRITER}

28:

29:

ACQUIRE_GL()

\triangleright activate fallback

30:

WAIT_FOR_READERS()

31:

else

32:

go to 2

33: end function

34: function CHECK_FOR_READERS

for i \leftarrow 0 to N-1 do

\triangleright Abort if any thread...

35:

\triangleright ... is an active reader...

if state[i] is #READER then

36:

37:

TX ABORT()

38: end function

39: function WAIT FOR READERS

for i \leftarrow 0 to N-1 do

\triangleright For every thread...

40:

repeat until state[i] \neq \#READER

41:

\triangleright wait until it is not an active reader

42: end function

```

cuting in HTM, SpRWLock uses the following mechanism. Before a reader *tid* is granted access to the read critical section, it first advertises its existence to concurrent writers in the *tid*-th entry of the *state* shared array. The update of the state array is followed by a memory fence, which, as we will discuss, is key for correctness,

Figure 3.1: A read access during an active update transaction will abort the latter.

| R-begin | r(x)=0 r(y)=0   | R-end       |               |

|---------|-----------------|-------------|---------------|

| W-begi  | n w(x=5) w(y=7) | 7) W-checkR | W-commit<br>→ |

Figure 3.2: A read access which commits before an active update transaction writes on shared values or verifies the state allows it to successfully commit.

as it ensures that the state of readers is globally visible before they enter the read critical section. Upon releasing the read lock, the reader's state is accordingly reset — this time without recurring to memory barriers, though.

Writers, in their turn, check for the existence of concurrent active readers, by inspecting the *state* array, upon requesting to release the write lock, i.e., before attempting to commit the corresponding HTM transaction. Only in case no reader is found active, the HTM transaction can be committed; else, the writer is forcibly aborted and restarted (see Fig.3.1).

This mechanism ensures that no writer can commit and materialize any changes to memory if there is any concurrent, active readers. This, in turn, guarantees that readers execute on isolated snapshots of memory, despite they can run concurrently with HTM-backed writers, as illustrated in Fig. 3.2, as well as with other readers.

In the above description, we have, for simplicity, omitted discussing the management of the fall-back execution path, which, we recall, is required in HTM systems to ensure termination of transactions that cannot be successfully executed in hardware. As in typical HTM systems, SpRWLock uses a *single\_global\_lock* (SGL) as fall-back synchronization method: in case a transaction cannot complete successfully in HTM after some predetermined number of attempts, the transaction is executed pessimistically, after having acquired the SGL. SGL is also *subscribed* right after a hardware transaction begins, i.e., the lock's state is read and the transaction is aborted if the lock is not found free. This guarantees that if a thread activates the fall-back path and acquires the SGL, any concurrent hardware transaction is immediately aborted.

In order to ensure the correct interplay between un-instrumented readers and writers active using the SGL, readers check the SGL after flagging their own state to active, and are allowed proceed only if the SGL is found free (see line 13). The writers that execute in the fall-back path, in their turn, have to wait for the completion of any active reader after acquiring the SGL and before executing the write critical section (see line 2). Overall, this mechanism ensures safety by precluding any concurrency between un-instrumented readers and writers executing in the SGL.

As we will show, despite its simplicity, this base algorithm is surprisingly effective in boosting system's throughput in workloads dominated by long readers that do not fit HTM's capacity. Indeed, if one attempted to use plain HTM to elide a read critical section that does not meet the hardware capacity limitations, the reader would eventually exhaust its budget of retries using HTM and acquire the SGL fallback. This would prevent any concurrency with other readers and/or writers. Conversely, with SpRWLock, readers that exceed HTM's capacity can still execute concurrently not only with other readers, but also with other writers executing in HTM, as exemplified by Fig. 3.2.

However, since writers are only allowed to commit using HTM in absence of concurrent readers, in read intensive workloads, this base algorithm exposes writers to the risk of starvation. More precisely, this approach can expose writers to the risk of exhausting their budget of retries in HTM, leading to frequent activations of the pessimistic fall-back path that can hinder not only the latency of writers, but also the global degree of concurrency in the system.

## 3.2 Scheduling Techniques

In order to address the above discussed shortcomings, SpRWLock integrates two additional scheduling techniques, which we refer to as reader and writer synchronization schemes. The former imposes delays on the readers' side, in case they detect active writers, whereas the latter imposes delays to writers, if they detect active readers. The two synchronization schemes operate in a synergistic fashion, ultimately aimed to enhance SpRWLock's efficiency, but they do pursue different goals.

Specifically, the reader synchronization scheme pursues a twofold goal: i) providing fairness guarantees for the writers, by ensuring that newly readers cannot cause the abort of already active writers, and ii) reducing the. The writer synchronization scheme, conversely, stalls writers to prevent them from uselessly consuming their budget of attempts using HTM, while striving to achieve maximum concurrency with any active reader.

Also, in this case, we present the two techniques in an incremental fashion, introducing first the reader synchronization scheme and then the writer synchronization mechanism.

### 3.2.1 Reader Synchronization

The pseudo-code of the reader synchronization scheme is reported in Alg. 3. Note that the pseudo-code illustrates only the differences with respect to the base algorithm, omitting the parts in common. This variant uses two additional shared arrays, also having one entry per each thread in the system:  $clock_w$ , which stores the expected end time of any currently active writer, and  $waiting_for$ , which is used by readers to advertise the identity of any writer they are currently waiting for.

In order to estimate the expected end time of (write) critical sections in a lightweight, yet accurate, fashion, SpRWLock relies on the hardware time stamp counter, which in modern CPUs provides a low-overhead, cycle-accurate time source.

| 111 | <b>Solution of the addition of t</b> | Some (uncad via)                              |  |  |  |

|-----|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-----------------------------------------------|--|--|--|

| 1:  | Shared variables:                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                    |                                               |  |  |  |